ThreadRipperに並ぶ性能のXeon-W

AVX512命令などではThreadRipperを上回る

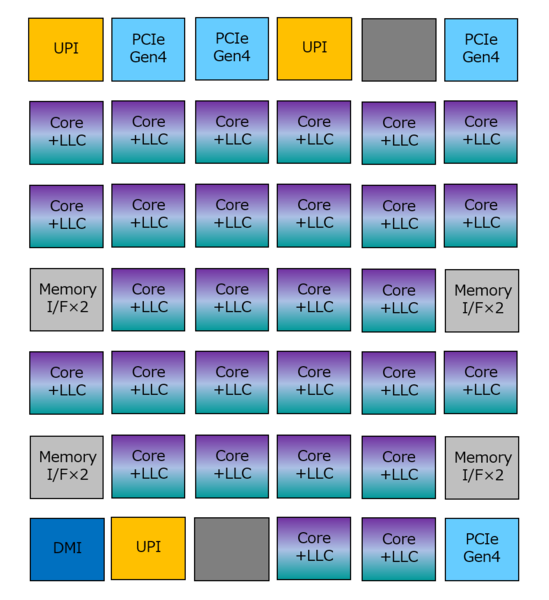

そのIce Lake-SPの構成は連載578回で説明したが、これを簡略化したのが下図である。

6×7で42モジュールの構成で、うちUPI×3、PCIe×4、DMI×1、メモリーコントローラー×4の合計12のモジュールが必要なので、コアそのものは最大30内蔵可能だ。ただし冗長コア領域かなにかで2コア分は無効化されており、合計28という計算だ。

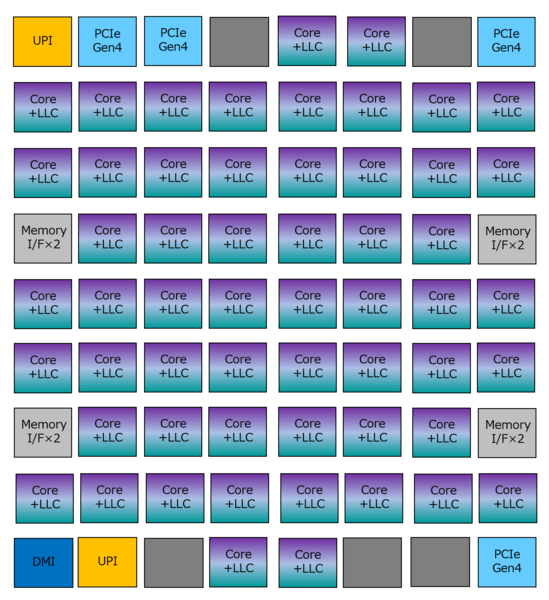

ではこれと同じ仕組みで56コアを作ったらどうなるかというと、最低でも56コア+12のその他のモジュールで68モジュール分が必要になる。17×4というのはダイが無駄に長くなるため、10×7で2モジュール冗長、あるいは8×9で4モジュール冗長というあたりであろう。どちらかといえば8×9説を取りたいところである。理由は正方形に近いほど、個々のコアとメモリーコントローラまでのHop数のバラつきが減るためだ。

すると構造は下図のようになる。この図がHCC構成、先の図がMCC構成で、他に16コア程度のLCCもあるかもしれない。

このIceLake-SPは、おそらくXeon-Wの形でワークステーション向けに投入されるとは思うのだが、これをCore-Xとして投入する気配は今のところ見られない。これに関しては完全にAMDのThreadRipperに喰われてしまった感があり、むしろXeon-Wに一本化する形になりそうな気配が強い。

実際AMDにしても、ThreadRipperは完全にワークステーション向けとなり、むしろThreadRipper Proというブランドを新たに追加したあたりはXeon-Wの対抗馬という位置づけになっているわけで、Core-Xを無理して維持する必要もないのだろうと想像する。

そのXeon-W、ローエンドの1ソケット向けには現在のComet Lakeに代わってRocket Lake-Sが入るだろうが、その上は全部Ice Lake-SPで切り替えになりそうだ。Whitley Platformベースで、パッケージはLGA 4189、DDR4-3200×8chとPCIe Gen4が出る強力なプラットフォームである。

実際カタログスペックで言えばThreadRipperに並ぶ構成だし、コア数も最大56だからThreadRipper/ThreadRipper Proの64と大差ない。AVX512命令やDL Boostなどを駆使した場合の性能は間違いなくThreadRipperを上回るだろう。

このXeon-W、ロードマップ図には4月頃?と書いたが、深い根拠があって書いているわけではなく、3月はメインストリーム(=2ソケット)向けのXeonの立ち上げが忙しいので、発表は3月でも出荷は4月頃ではないかと見当をつけているだけである。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ