新年になったので、今週から久々にロードマップのアップデートをお届けしよう。といっても後述するように、来週のCESでもう少しいろいろ話が出てくるとは思うのだが、これに先んじて判明している範囲で解説していく。

Ice Lake-SPのXeon-Wが4月頃発売

最大コア数は56?

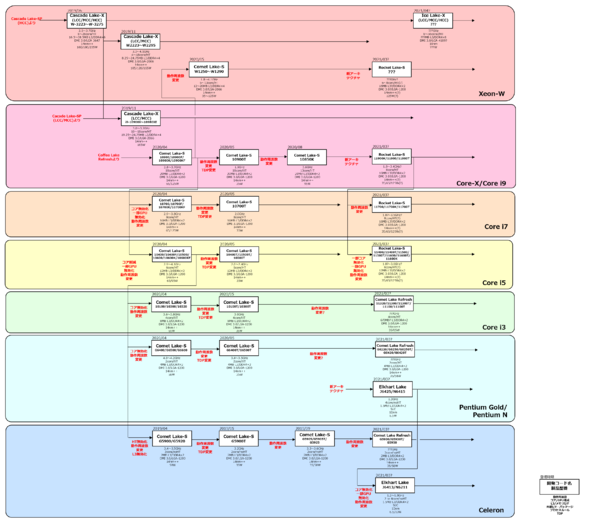

ロードマップそのものは連載585回に出したものと「ほぼ」同じである。もう少しRocket Lakeに関する詳細が明らかになったので、これを埋める程度である。上から順に説明しよう。

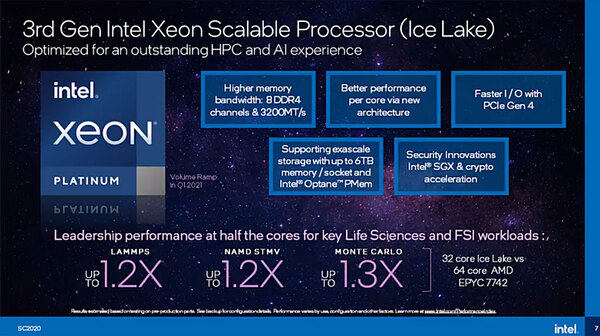

まずXeon-Wについてだ。こちらは、おそらくIceLake-SPをベースにしたもので置き換えるはずだ。Hot Chipsでは最大でも28コアまでの構成しか示されなかったのだが、2020年11月にオンラインで開催されたSC 2020においてインテルはIce Lake-SPベースの32コアCPU×2の構成が、EPYC 7742×2よりも高速という説明をした。

対象は64コアのEPYC 7742×2のシステムで、これを32コア IceLake-SP×2のシステムと比較したそうだ。Ice Lake-SPの方は動作周波数2.2GHzで、メモリーはどちらも256GB DDR4-3200だそうである

性能そのものはLAMMPSで1.2倍、NAMD STMVでも1.2倍、Monte Carloで1.3倍、Ice Lakeの方が高速というもので、Ice Lakeの方が稼働コア数が少ない(ちょうど半分)のに1.2~1.3倍高速というアピールである。

ただこれはAVX512に最適化されたベンチマークという面があるので、AVX512に未対応なEPYCが遅いのはある意味当然である。それより問題はこれが32コアだということだ。

そもそもIce Lakeは最大何コアまで用意されるのか? という話で、公式には一切発表がないのだが、筆者は56コアではないかと想像している。少し前の話になるが、2019年8月にCooper Lakeが発表されたときのリリースで、2020年前半には標準的なソケットに装着できる56コア製品を投入する、と豪語した話は連載524回で説明した通りだ。言うまでもなくこんな話はどっかに消えてしまったわけだが、実は先のリリースをよく読むと、

- Cooper Lakeは“Next Gegeneration Intel Xeon Scalable Processor”である。

- 2020年前半にはNext Generation Xeon Scalable Processorで56コアの製品を出す。

とは書いてあるが、“Next generation Xeon Scalable ProcessorはCooper Lakeだけである”とはどこにも書いてない。

実際この第3世代、当初はCooper LakeとIce Lakeの両方が同時に投入予定であった。となれば、56コアはIce Lake-SPで実現予定だったとしても不思議ではないというか、他に考えようがない。14nmのCooper Lakeで56コアが実現できると考える方がどうかしているというべきか。MCM構成で56コアを無理やり実現したCascade Lake-APを見ていれば、あれを標準のソケットに収めるのはどう見ても無理というのは容易に想像がつく。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ