ロードマップでわかる!当世プロセッサー事情 第590回

Radeon Instinct MI100が採用するCDNAアーキテクチャーの内部構造 AMD GPUロードマップ

2020年11月23日 12時00分更新

11月20日、「Radeon RX 6800」シリーズが無事に発売になった。KTU氏によるレビューをご覧になった方も多いと思うが、おそろしくパワフルな製品に仕上がっており、レイトレーシングを利用しない限りにおいてはGeForce RTX 3000シリーズに十分競合できる。

という話はおいておき、今回解説するのは11月16日に発表されたCDNA第1世代を実装する、Radeon Instinct MI100の話である。が、その前に連載587回に誤りがあったため、まずはこれの訂正をしたい。

Smart Access Memoryを利用するのに必要な

Resizable BAR

こちらでSmart Access Memory (SAM)の正体はCCIXを利用したCoherent Memory Accessではないかと推察したのだが、その後AMD本国の関係者から「そうではなく、PCIeでの接続である」という返事が返ってきた。

その後にSAMを利用するためにはBIOSセットアップでを有効にすべしという注意書きが届いて、やっと正体がわかった格好だ(KTU氏もレビュー記事で触れている)。ついでなので、このResizable BARの話をしよう。

BAR(Base Address Register)というのは、PCI ExpressのConfiguration Space(PCI Expressのデバイスを内部で管理するためのメモリー空間)の中にあり、デバイスのメモリー領域をホスト(つまりCPU側)のメモリー空間にマッピングする際のアドレスを格納している。

もともとはPCI Express(の元になったPCI)が32bitアドレスでの動作を想定していたこともあり、BARの扱えるメモリー領域は最大でも256MBに制限されていた。ところが64bitアドレッシングをサポートしたCPUが登場したことで、BARをもっと広げても良いのではないか? という議論が起こる。

最終的にPCI Express 2.0のECN(Engineering Change Notice)として2008年1月22日に、Resizable BARという仕様が追加された。これはBARのサイズを最大512GBまで拡張できるというもので、オプション扱いとなり、PCI Express 2.1以降では正式に仕様に取り込まれているみ(ただし実装は必須ではなく引き続きオプション)。

マイクロソフトはWDDM v2でこのResizable BARに対応したことを2017年4月に表明している。というわけで、SAMは別にDX12やVulkanだけでなく、DirextX 9/10/11やOpenGLでもその効果が期待できるとAMDの関係者からは返事があった。

余談であるが、筆者もHorizon Zero DawnをSAMありで実施したが、問題なく4Kで完走した。KTU氏との違いは、主にマザーボード(筆者はASUS ROG CROSSHAIR VIII HEROを利用)程度であるが、それが理由とも思えないのだが。

CDNAアーキテクチャーを採用したHPC向けGPU

AMD Instinct MI100を11月16日に発表

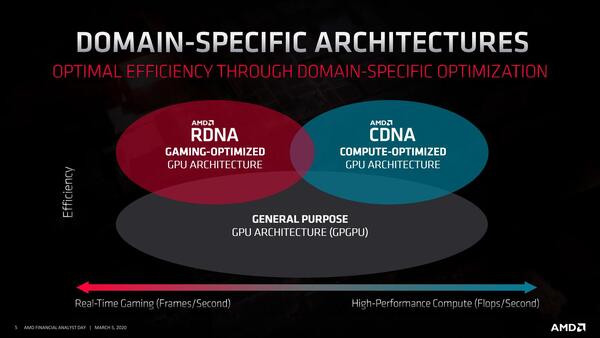

さて、Radeon RX 6800の話はこの程度にして、本題に入ろう。もともとRadeon Instinct系、つまりGamingではなくComputationにフォーカスした市場向けに、AMDは従来のGCN(Vega)からRDNA(Navi)とCDNAに分けると今年3月に明らかにした。

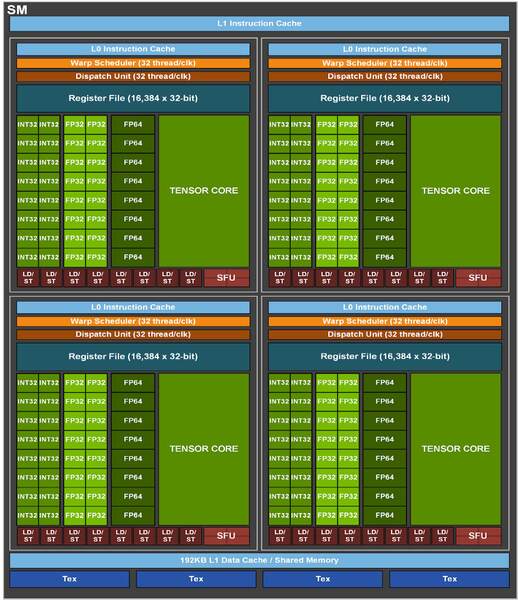

これはNVIDIAも同じで、アーキテクチャーこそ共通のAmpereとされつつ、GPGPU向けのGA100とGaming向けのGA102では、SM(Streaming Processor)の構造が異なっている。GA100はFP64の演算ユニットを搭載する一方でRTコアがなく、逆にGA102はFP64を省いてRTコアを搭載しているのがわかる。AMDはもっと大胆に、アーキテクチャーそのものを切り替えた形だ。

さてその中身である。ちなみにAMDはまだ“VEGA”や“NAVI”にあたる、CDNAのコード名を公開していない。“Arcturus”という名前がRadeon Instinct MI100のコード名と言われているが、アーキテクチャーの名前そのものではない。ということで、以下CDNA 1.0として表記したい。

そのCDNA 1.0の構造が下の画像となる。RDNAの構造と比較すると、(CU数はともかくとして)例えばPixel UnitやRasterize、RB(Render Backend)など描画に必要な要素がキレイに消えていることがわかる。また、当然ながらGeometry Processorも搭載されていない。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ