32Bytes幅のDual Ringを採用

実質的な帯域はIce Lakeの2倍以上

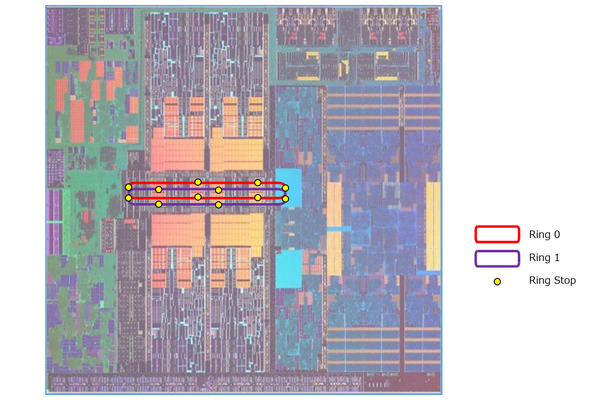

次いでDual Ringの話。下図はPhelp氏の説明をもとにおこしたものだが、UncoreからCPUとGPUで別々のRingにするのではなく、UncoreとCPUコア、およびGPUコアをすべてまたがる形でRingが構成されているが、ただしそれが二重になっているというものだ。なので、それぞれのCPUコアやGPU、Uncore部はすべて2つのRing Stopを持つ形になる。

ちなみにRingそのものは従来と同じ32Bytes(256bit)幅である。この2つのRingを、それぞれのCPUコアなりGPUなりは自由に利用できる。つまり、ピークでは64Bytes(512bit)幅のデータアクセスができることになる。AVX512のLoad/Storeなどが1サイクルで行える形だ。

「だったらいっそ64Bytes幅のRing1つでも良かったのでは?」と尋ねたところ「それではRing Stopまでが遠くなりすぎる」との返事。

256bit幅のRingと512bit幅のRingでは配線の難易度が変わってくるのは明白で、実装を考えると256bit×2の方が楽だったのだと思う。

ただ、すでにSandy Bridgeあたりの世代からキャッシュラインは64Bytesになっているので、CPUからのアクセスという意味では64Bytes幅の方が実装は楽だとは思う。

実効性能という意味では、Ice Lakeでは内部のRingの速度は最大3GHzとなっており、一方Tiger Lakeではこれを超える速度で動いているそうで、実質的な帯域は2倍を超えることになる。

もっともTiger Lakeの世代ではその分、GPUからメモリーコントローラーに最大64GB/秒の帯域保障を提供する(一種のQoS)機能なども実装されており、これをフルに使った場合は片方のRingの帯域の半分以上(多分2/3近く)が占有されてしまうことになるため、Dual Ring化は必須だったとも言える。

そのDual Ringに絡んでもう1つおもしろい機能がIO Cachingだ。これは「I/OデバイスがLLCに直接アクセスできるもの」だという。

通常I/Oはメモリーに対してDMA(Direct Memory Access)を利用してデータの転送を行なう。例えばSSDから読み込んだファイルの内容は、SSDの内容をSSDコントローラー→PCI Express経由でまずメモリーに格納され、次いでそのメモリーの内容をCPUが読み込むという順で行なわれる。

DMAはその名の通り、直接I/OデバイスがCPUを介さずにメモリーを読み書きできる機能で、これにより無駄にCPUを使わずにデータ転送が完了するのだが、いちいちメモリーに書き込んで、また読み出すのは時間がかかる。

IO CachingはDMAの対象をメモリーではなくLLCに行なえるというものだ。これにより、CPUはメモリーアクセスなしで直接LLCからデータを読み込めるようになる。

もっともこの仕組み、ドライバー側でこれにきちんと対応しないといけない。またIO Cachingに利用されるLLCは排他(通常のキャッシュ領域とは分けて考える)にしないといけない。

データがやってきてからおもむろにキャッシュを確保していたら、そのレイテンシーの方がメモリーアクセスより遅くなりかねないためだ。となるとOS側の対応も必要になりそう(少なくともプラットフォームのCPU用ドライバーに手を入れる必要はある)である。

加えて言えば、上の例でこのIO Cachingを有効にすると、ファイルアクセスの場合はメモリーではなくLLCを参照するようにしないといけないわけで、これはOSそのものにも関係しそうな気がする(ファイルシステム周りのデバイスドライバーの改修だけで済めばいいのだが)。

以上のことから、これが実際に利用できるようになるのにはやや時間がかかるだろう。とりあえずTiger Lake搭載ノートが市場に出たとして、その時点でのWindows 10はおそらくIO Cachingには対応できないだろう。このあたりの対応スケジュールはインテルというよりもOSベンダーに確認する必要があるだろう。

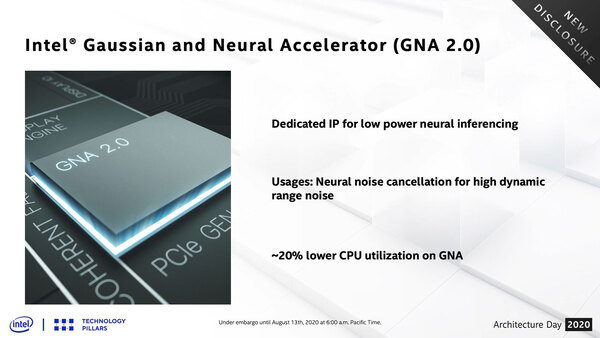

そういえばGNA(Gaussian and Neural Accelerator) 2.0であるが、2.0になっても新機能や機能拡張といったことは一切なく、純粋に性能と性能/消費電力比を改善した「だけ」とのこと。

もっとも性能は最大30GOP/秒に達しており、消費電力の改善やCPU負荷率の低減などと相まって、より使いやすくなったそうだ。

実際Tiger Lakeでの発表会においても、ノイズキャンセリング機能への実装(テレビ会議をしている人の後ろで掃除機がかけられていても、話者の声が明瞭に相手に届く)という形でそれがデモされていた。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ