連載577回でTiger Lakeについて説明したが、記事を上げた後で、開発者の1人であるBoyd Phelps氏に、電話会議の形で30分ほど話をうかがう機会が得られたので、この内容を中心に前回の記事のアップデートをお届けしよう。

ちなみにBoyd Phelps氏、肩書はVP Client Engineering Group, GM Client and Core Development Groupになっているが、実際にはTiger Lakeの設計やシステム全体の最適化(コアそのものはWillow Coveで、これは先日辞任したJim Kelly氏の責任範囲)に携わっていたらしい。そういう意味では、Tiger Lakeの内部の詳細を確認するのに一番適切なお相手であった。

TDP表記をやめOperation Rangeに変更

放熱能力ではなく供給電力の限界を提示

さて、まずは動作周波数に関する話。Tiger Lakeのスペックそのものはジサトライッペイ氏の記事で詳しく説明しているので繰り返さないが、実はインテルはTDPという用語をTiger Lakeで使うのはやめ、Operation Rangeなる用語を採用した。

したがってイッペイ氏の「Tiger LakeはTDPによってUP3(12~28W)、UP4(7~15W)の2系統存在する」という文章は厳密には正しくなく、正確には「Tiger LakeはOperation RangeによってUP3(12~28W)、UP4(7~15W)の2系統存在する」となる。

そもそもなぜTDPという言葉を使うのを止めたのかという質問に対する回答は「Tiger Lakeでは、12~28WのUP3と、7~15WのUP4の2種類が用意されるが、ダイそのものはどちらも共通で、(消費電力が)低い所から高い所まで同一のダイでスケーラブルに対応できる。Operation Rangeの限界は、実はダイそのものではなくパッケージに依存する」そうである。

TDPはもともとThermal Design Power、つまり消費電力が熱にすべて変わることを前提に、何Wの熱源として捉えるべきかという指標として提供されているもので、放熱能力の限界がそのまま動作周波数の限界となっていたわけだが、今回の場合は放熱能力の限界なのではなく、パッケージの供給電力のレンジの限界が7~15Wなり12~28Wということになる。

それもあって、TDPという言い方ではなくOperation Rangeに切り替わったそうだ。

加えて言えば、「実際の放熱能力の限界というのは、OEMベンダーのデザイン(=筐体設計)次第で変わってくる」という話で、放熱能力の限界そのものは当然存在するが、それは各ベンダーで異なる数字であって、インテルからはOperation Rangeという言い方で消費電力枠を示し、あとはベンダーが自身の熱設計に合わせて動作周波数を選択するという形になったのだそうだ。

もっともインテル自身もこのあたりは完全に整理されていないようで、Intel ArkのCore i7-1185G7を見ると、Configurable TDP-up/downという表現が残されている。そのうちこのあたりもRange upper/Lower limitなどの表現に変わるのかもしれないが、とりあえずSpecificationを見ても、まだTDPという用語が残されているようで、このあたりが整理されるまで時間がかかりそうだ。

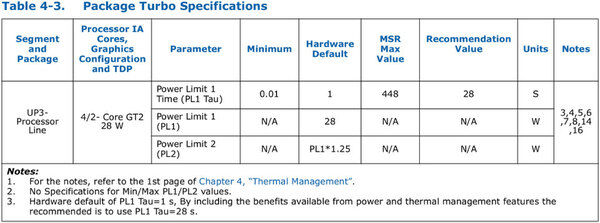

ちなみに気になるPL2の値であるが、SpecificationによればPL1(=28W)の1.25倍で35W、PL1 Tauはデフォルトで28秒と比較的穏当な数字であった。

ノート向けだとデスクトップと異なり、PL2をPL1の2倍などにはできないし、長時間連続も厳しいので、穏当にならざるを得ないのは理解できる

画像の出典は“11th Generation Intel Core Processor (UP3) Datasheet, Volume 1 of 2”

キャッシュは容量の問題で

MLC/LLCからNon-inclusiveに変更

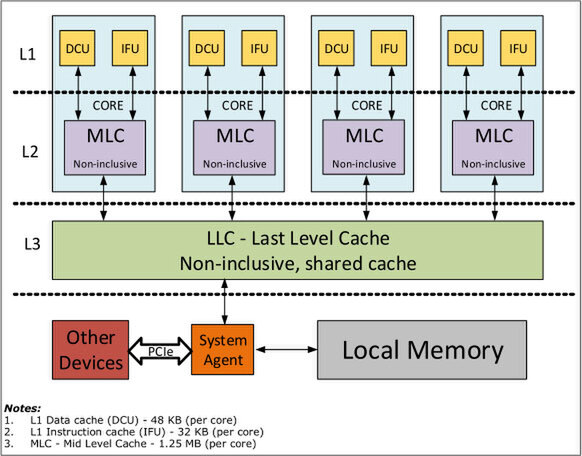

次にキャッシュだ。連載577回で紹介したように、Tiger LakeではMLC/LLCがNon-inclusiveに変更された。この理由を確認したところ、やはり容量の問題とのこと。

さすがにL1のIFU/DCUはInclusiveのままである。ここをNon-Inclusiveにすると、性能へのインパクトが大きいし、そのわりに稼げるキャッシュ容量は大して大きくないからだろう

画像の出典は“11th Generation Intel Core Processor (UP3) Datasheet, Volume 1 of 2”

Tiger LakeはMLCが1.25MB/コア、LLCが3MB/コアであるが、Inclusive方式にしてしまうと、MLCの中身はLLCと完全に同一になるため、実質LLCが1.75MB相当になる計算である。

それでもIce Lakeまでの世代に比べると若干は増えている(Ice Lakeは512KB MLC/2MB LLCなので、実質1.5MB LLC/コアという計算になる)が、競合のZen 2ではコアあたり4MBのLLCを利用できることを考えると、大きな差が付いていることは否めない。

もっともZen 2ではMCM構成でメモリーコントローラーまでのアクセスが遅くなるため、これを補うための大容量3次キャッシュという側面もあるので同一に比較するのはどうかとも思うのだが、やはり効率的な利用を考えた場合はMLCとLLCをNon-Inclusiveにする方が適当、という判断だったらしい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ