ロードマップでわかる!当世プロセッサー事情 第566回

マルチメディア向けからAI向けに大変貌を遂げたMovidiusのMyriad 2 AIプロセッサーの昨今

2020年06月08日 12時00分更新

製品化されずに終わったSHAVEが

Myriad 2として復活

さてそんなわけで登場したSHAVEであるが、これが製品化されたかというと、どうも製品化はうまくいかなかったらしい。

少なくとも28nmのFragrakは、実際には製造されずに終わったようだ。加えて言えば会社の役員にも変更があった。

もともとMovidiusはSean Mitchell氏とDavid Moloney氏が立ち上げた会社で、Mitchell氏がCEO、Moloney氏がCTOという役割を果たしていたが、2013年5月にCEO職をTIから来たRemi El-Ouazzane氏にバトンタッチ、Mitchell氏はSVP兼COOに降格した。

そして新しいCEOの元でMovidiusはビジネスの方向性を転換する。2014年1月の同社のトップページから、Productsページが消えているのがわかる。

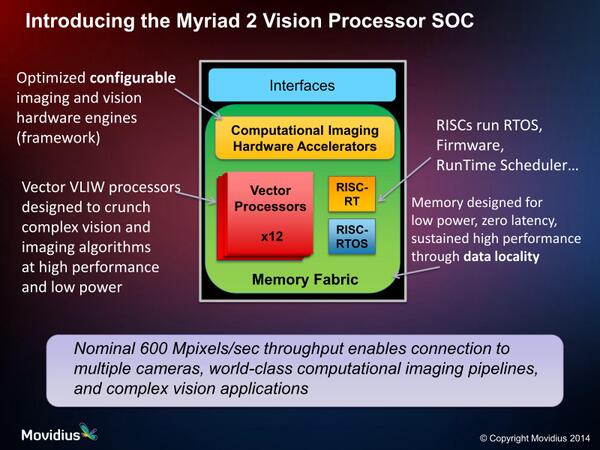

その新しい方向性が明らかにされたのは、実は2014年のHot Chips 26である。ただこの時、新製品であるMyrad 2はVision Processor SoCとして発表された。

基本的な構成はSHAVEそのままで、ただしVectorプロセッサーが12に増えたのと画像処理ハードウェアが追加されたのが大きな違いだ。

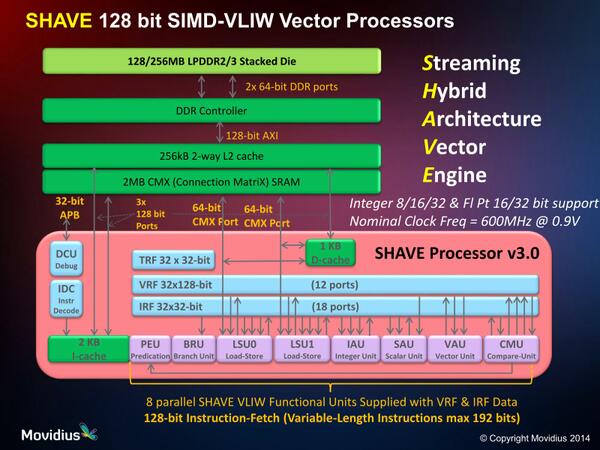

Vectorプロセッサー、つまりSHAVEコアだが、基本的な構成は従来の構造を引き継いでいるものの、Vectorサイズが128bitになり、またSRFが廃された(IRFを共通で使うようにした模様)。

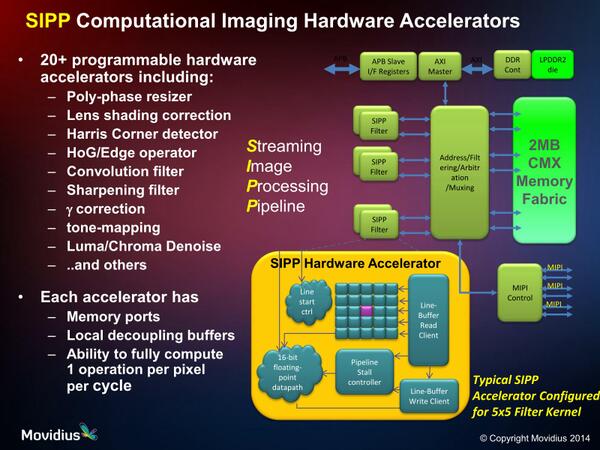

データ型は8/16/32bit Integerと16/32bit Flotをサポートする。一方画像処理ハードウェアは下の画像の通りで、さまざまな画像処理フィルターをハードウェアで搭載しているとされる。

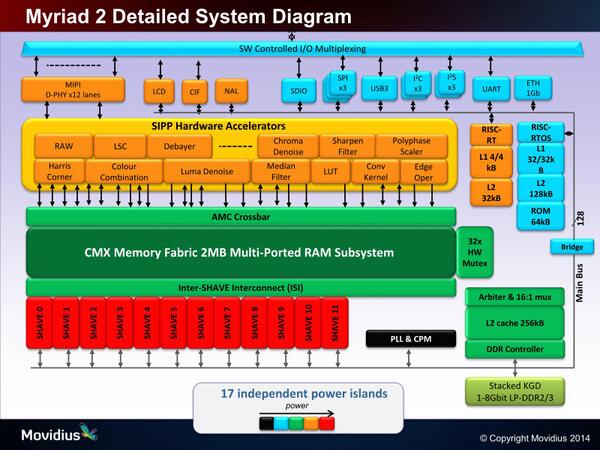

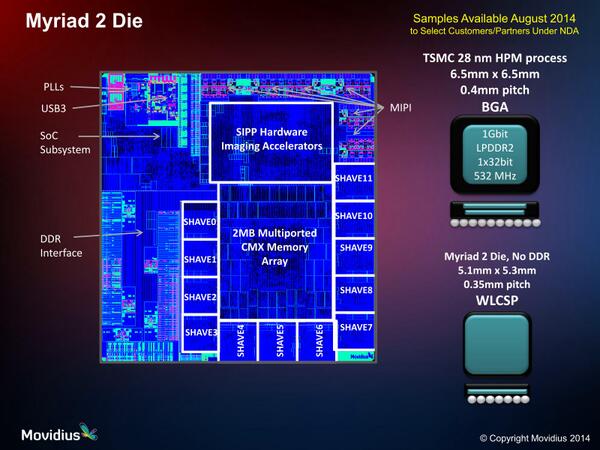

最終的なMyriad 2の全体の構成が下の画像である。TSMCの28HPMで製造した場合、ダイサイズは5.1×5.3mmで27mm2に抑えられるとしている。

消費電力については、30fpsの画像処理(入力画像サイズは不明)の処理が250mW未満で可能という話であった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 - この連載の一覧へ