ピーク性能よりも性能/消費電力比を重視

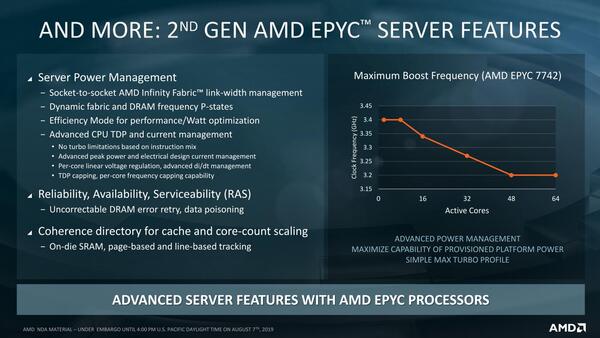

最後に動作周波数周りの話をする。たとえばハイエンドになるEPYC 7742の場合の動作周波数とActive Core数の関係は下の画像のようになっている。

ピーク性能よりも、平均性能あるいは性能/消費電力比を悪化させない、というのがパフォーマンスの基本になっており、命令セットによる消費電力調整がない(インテルのAVX2/AVX512オフセットに相当するものがない)というあたりも、無理に動作周波数を引き上げていないことが見て取れる。

性能はむしろコア数で稼ぐ方向であり、このあたりは7nmプロセスにしたことで、コア数にゆとりが出たこ事の反映とみて良いだろう。

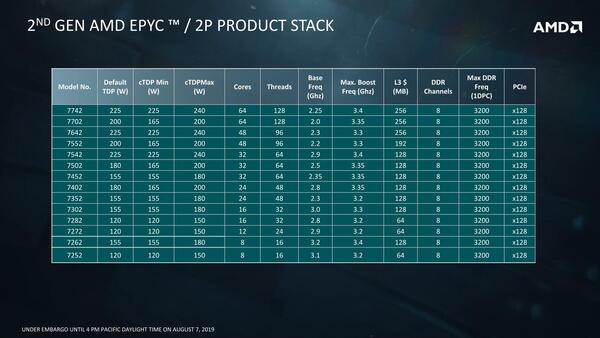

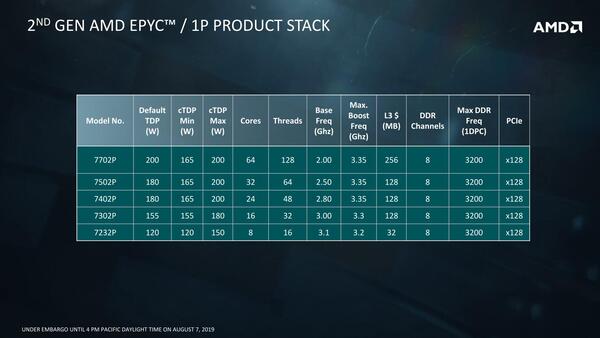

製品のラインナップであるが、下の画像が2 Socket向け、さらにその下の画像が1 Socket向けである。この2 Socket向けについて初代のEPYCと混ぜる形で動作周波数およびTDPをまとめたのが表である。

| 第1世代と第2世代EPYCの動作周波数およびTDP(太字が第2世代) | ||||||

|---|---|---|---|---|---|---|

| モデルナンバー | コア数 | ベースクロック(GHz) | 最大ブースト クロック(GHz) |

最小cTDP(W) | デフォルトTDP(W) | 最大cTDP(W) |

| 7251 | 8 | 2.10 | 2.90 | 120 | ||

| 7252 | 8 | 3.10 | 3.20 | 120 | 150 | |

| 7261 | 8 | 2.50 | 2.90 | 155 | 170 | |

| 7262 | 8 | 3.20 | 3.40 | 155 | 180 | |

| 7272 | 12 | 2.90 | 3.20 | 120 | 150 | |

| 7281 | 16 | 2.10 | 2.70 | 155 | 170 | |

| 7282 | 16 | 2.80 | 3.20 | 120 | 150 | |

| 7301 | 16 | 2.20 | 2.70 | 155 | 170 | |

| 7302 | 16 | 3.00 | 3.30 | 155 | 180 | |

| 7351 | 16 | 2.40 | 2.90 | 155 | 170 | |

| 7352 | 24 | 2.30 | 3.20 | 155 | 180 | |

| 7371 | 16 | 3.10 | 3.60 | 200 | ||

| 7401 | 24 | 2.30 | 3.20 | 155 | 170 | |

| 7402 | 24 | 2.80 | 3.35 | 165 | 180 | 200 |

| 7451 | 24 | 2.00 | 3.00 | 180 | ||

| 7452 | 32 | 2.35 | 3.35 | 155 | 180 | |

| 7501 | 32 | 2.00 | 3.00 | 155 | 170 | |

| 7502 | 32 | 2.50 | 3.35 | 165 | 180 | 200 |

| 7542 | 32 | 2.90 | 3.40 | 225 | 240 | |

| 7551 | 32 | 2.20 | 3.00 | 180 | ||

| 7552 | 48 | 2.20 | 3.30 | 165 | 200 | |

| 7601 | 32 | 2.20 | 3.20 | 180 | ||

| 7642 | 48 | 2.30 | 3.30 | 225 | 240 | |

| 7702 | 64 | 2.00 | 3.35 | 165 | 200 | |

| 7742 | 64 | 2.25 | 3.40 | 225 | 240 | |

| ※太字が第2世代EPYC | ||||||

初代EPYCはモデルナンバーの末尾が1、第2世代は末尾が2となっていることでそれとわかる。比較してみると、たとえば同じ8コアの7251と7252では、ベース周波数が1GHz以上引き上げられているし、16コアの7301と7302でもやはり結構な引き上げになっている。

32コアの7501と7502では、さすがに7502が定格ではTDPが180Wになるので、Configurable TDPで165Wの動作モードを提供しており、この場合では多少最大動作周波数は落ちると思うのだが、それでもベース周波数は2.5GHzまで引き上げられているあたり、同じコア数であれば確実に動作周波数のアップが実現されている。

あるい初代EPYCの32コア製品である7501と、第2世代で64コアの7702を比較すると、ほぼ同じTDP(155W vs 165W)で同じベース周波数ながらコア数が倍増しているわけで、アップグレードによって確実に性能がアップしている(あるいは性能/消費電力比が大幅に改善している)ことが推定できる。

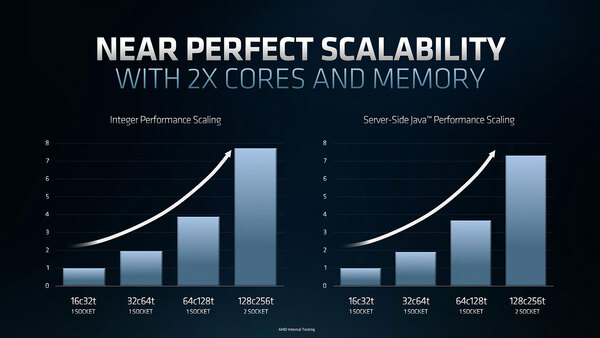

ところで先ほど触れた性能の話を。下の画像はInteger PerformanceとServer Side Javaの性能を比較したものだが、メモリー帯域が8chのままでもほぼコア数が倍(32c64t→64c128t)になると性能が倍増しているあたりは、大容量3次キャッシュが良い仕事をしているということだろう。

このあたりは実アプリケーションで検証の必要はあるのだが、AMDによればメモリーが8chのままでも十分スケールするというのが第2世代EPYCに対するメッセージということである。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ