40bitもの巨大な仮想アドレスを保有

ただしなぜ40bitにしたのか謎

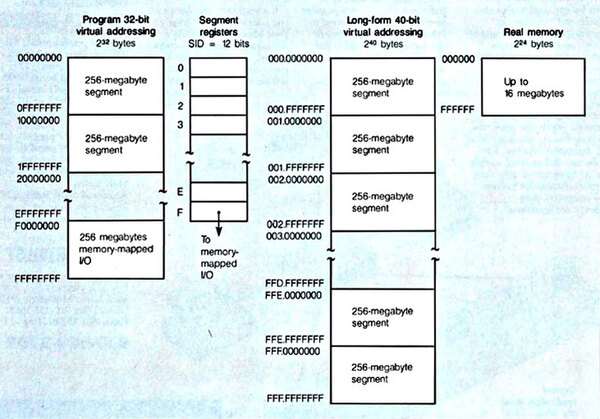

ROMPの仮想記憶は、物理的なメモリーは最大16MBまで対応ながら、仮想アドレスは40bitという結構巨大なサイズである。ただしこれ、12bit(0~4095)のセグメントに分かれた28bit(256MB)のメモリーエリア、というややおもしろい構成である。

画像の出典は、Internet Archives保有のBYTE Magazine Volume 11, Number 11の“Inside the IBM PCs”という特集号

ページサイズは2KBで、12bitのセグメントIDと17bitのページナンバー、11bitのページ内オフセットという形になる。まだこの当時、この40bitをフルに利用できるOSは存在していないが、それに向けて32bitの仮想記憶マシンとして使うことももちろん可能だった。

ただ逆に言えば、なぜ40bitの構成にしたのかの説明がついぞ見つからなかった。強いて 言えば、IBM System Journalの中に“ROMP is a good architectural base for future growth”(ROMPは将来の発展のベースとなる良いアーキテクチャーである)という文言があるあたり、この当時はROMPをベースに製品を展開していくつもりだったのかもしれないが、発展する前にROMPそのものの寿命が尽きたあたりが皮肉ではある。

最終的にROMPは1981年、2チップ構成で完成した。プロセッサー本体は4万5000トランジスタでダイサイズは58.52mm2、MMUが6万1500トランジスタでダイサイズは81.36mm2である。

先に書いた通り、どちらもIBMの2μm NMOSプロセスで製造されている。ソフトウェアとしては、こちらもまずPL.8が移植され、次いでこれを利用してさまざまな言語が移植されることになった。先ほどの4.3MIPSやIBM 801の15.1MIPSという数字は、いずれもPL.8を利用した場合の数字である。

画像の出典は、Wikipedia

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ