16FFCをさらに低コスト化した12FFC

ただし技術的には16FFCとほぼ同一

16FFCに続いて今年の3月に発表されたのが12FFCである。12FFCの特徴は以下のようになる。

- 16FFCをOptical Shrinkにより微細化。これにより、既存のマスクそのままで微細化可能

- 新しい6トラックのCell Libraryを利用する(つまり7.5/9トラックのCell Libraryを使うと12FFCではなくなってしまう)

ちなみにこの6トラックのCell Libraryには、以下の2種類が提供される。

- 16FFCと比較して1.1倍の動作周波数改善、もしくは30%の消費電力削減ができるStandard Cell Library

- Dual Pitch BEOL(トランジスタの上の配線層:Back End of Lineのピッチを従来の倍にした)とトランジスタの性能アップにより、1.1倍の動作周波数改善もしくは20%の消費電力削減に加え、10%のエリア面積削減が可能なTurbo Cell Library

このうちOptical Shrinkというのは、露光の際に若干小さく露光を行なうことでエリアサイズを削減するという技法で、かつては90nm→80nmにOptical Shrinkが採用されていた。

ただ昨今は単純に微細化できないので(トランジスタの寸法をやや変えただけで特性が変わってしまう、配線層が十分細いので、これ以上細くすると配線抵抗が増えてむしろ性能が悪化するなど)、あまりOptical Shrinkという話は出てこなかった。

特にFinFETになるとFinの高さも絡んでくるからで、単純に縮小したらまともに動くかどうかも怪しい。ところがTSMCによれば「デザインルールも同じで、レイヤーもSRAMセルの構造も電圧レンジもI/Oもまったく変わらない」とする。

答えは、これも連載413回で書いたが、このOptical Shrinkは数%のごくわずかなもので、ほとんど特性が変わらないからである。したがって、実際には性能改善や消費電力削減などは、ライブラリを6トラックに変更したことの効果が圧倒的に大きいようだ。

ちなみにCarrizoの時にはCell Libraryを小型化することで性能はむしろ落ちているが、これはもともとのプロセスが高性能向けだったことに起因する。

今回はもともと性能を落とした16FFCがベースなので、Cell Libraryを小さくしたことで性能/消費電力比が改善しており、つまり消費電力が一定なら10%程度の高速動作が可能になった、と判断すべきであり、Voltaのようにもともと高性能向けのプロセスにこれを適用しても、むしろCellの数が増えるので性能は低めに推移することに注意したい。

それとTSMCは「16FFCと同じデザインで使える」と説明していて、嘘ではないのだが、実際には既存の7.5/9トラックのCell Libraryを6トラックに置き換えた時点でほぼ物理設計のやり直しになる。

TSMCの説明が正しいのは、TSMCのStandard Cell Libraryを使っていない(例えばARMのArtisanなど)場合であるが、この場合16FFCと12FFCの違いはOptical Shrinkだけなので、エリアサイズ縮小とか性能改善の効果はほとんど期待できないことになる。

プロセス的に見ると、16FFCと12FFCは技術的には同一である。こちらも長期的にはレイヤ1層あたりの処理は1日未満で終わることになり、しかも16FFCよりもエリアサイズを縮められる可能性があるので、より低コストのプロセスとなる。16FFCに代り、この12FFCをLong-Lived Nodeと言い出したのも無理ないところだ。

ロードマップ的にはこの後、やはり7nmについてもコンパクト版の7FFCを提供する予定であり、メインストリーム/バリュー向けの製品に関しては、16FFC→12FFC→7FFCというロードマップをTSMCは提示している。

逆説的に言えば、10nm世代に関してはTSMCもある程度見切りをつけており、広く利用されるプロセスにはなりえないと判断しており、ところが16FFCから7FFCに直接ジャンプだと時間が空きすぎる。かといって新しいノードを開発するのも難しい。

そこで、既存の16FFCとプロセス的には同じながら、ユーザーにメリットの出る形でのソリューションを探した結果が6トラックのCell Libraryの提供、というあたりに落ち着いたと考えるのが妥当なところだろう。

40ULPと28ULPは今年後半から量産開始

22ULPと12ULPは2018年量産開始

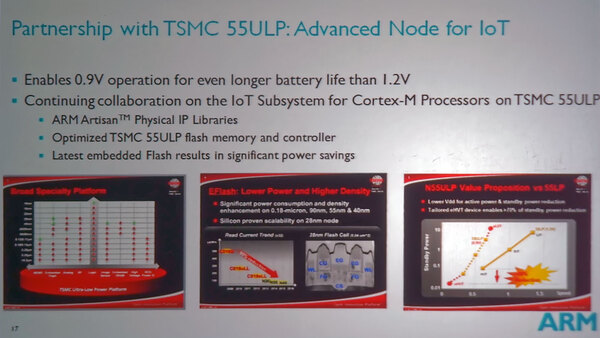

最後にローパワー/IoT向けについて。もともとこの分野では2010年代に入っても130nmや90nm、65nmといったプロセスが広範に使われていたが、2015年に55ULP(55nm Ultra Low Power)を発表した。

これは主にマイコンや、Wearable向けプロセッサーなどをターゲットにしたものだが、これに加えてTSMCは28nm世代の28HPC(28nm High Performance Compact:28HPという汎用プロセスの低価格版)の改良型で、低消費電力に向けた28HPC+を2016年に追加している。

55ULPと28HPC+の違いはEmbedded Flash(組み込みNOR Flash)の技術の有無で、マイコンを構成する場合はEmbedded Flashが必須なので55ULPを、そうでない場合は28HPC+をという形である。あるいは無線(WiFi/Bluetoothなど)を組み込む場合も28HPC+では製造できないので、55ULPでということになる。

ちなみに55ULPそのものの存在は2014年9月に発表されており、ここで55ULPだけでなく40ULP(40nm UltraLowPower)と28ULP(28nm UltraLowPower)も同時に発表されており、40ULPと28ULPは今年後半から量産開始の予定となっている。

これに続いて今年発表されたのが22ULPと12ULPである。22ULPは28ULPの延長にあるとしており、28ULPと比較して15%の性能改善もしくは35%の消費電力削減で、エリアサイズは最大10%縮小というあたり、ひょっとするとこの22ULPも28ULPに数%のOptical Shrink+6トラックのCell Libraryという組み合わせかもしれない。

こちらはすでにデザインはスタートしており、2018年に量産開始になると見られる。一方の12ULPは12FFCの省電力版と見られる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ