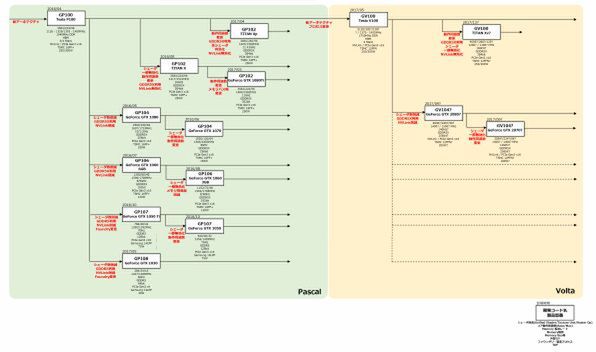

Volta世代のGV100コア製品を発表

Volta世代最初の製品がTesla向け、というのは予定通りであり、今年5月のGTCでTesla V100としてGV100コア製品が発表された。

とりあえずTesla V100は連載373回で解説したように、Power9と組み合わせる形でオークリッジ国立研究所のSummitとローレンス・リバモア国立研究所のSierraに納入が予定されている。まずはこれ向けの量産が最優先となる。

Summitの場合では、トータル4600ほどのノード1つあたり2つのPower 9と6つのVoltaが搭載されるので、まずは2万8000枚弱のVoltaカードをNVIDIAは量産せねばならない。Sierra向けも合わせると4万枚弱といったあたりで、これが一段落するまで少なくともGV100コアに関しては派生型などを考えるのは難しいだろう。

Tesla V100の12nm FFNプロセスは

16FF+に6トラックのスタンダードセルを適用

このGV100でもう1つ問題になるのはプロセスである。GTCの基調講演では“TSMC 12nm FFN”とあったが、実はこれはNVIDIA専用のカスタムプロセスである。まずこの話を改めてしておこう。

TSMCは16nm世代で大きく3種類のプロセスを用意した。16FF、16FF+、16FFCである。最初のものが16FFでFinFETの第1世代である。ただこれは量産前の試行とでもいうべきもので、量産製品のほとんどは16FF+という16FFの改良版を利用している。NVIDIAのPascal世代が全部これである。

この16FF+のコストを下げたコンパクト版が16FFCとなる。なぜか最新のTSMCの16nmのページでは説明が省かれているのだが、Googleのキャッシュに残された以前の説明によれば“TSMC also introduced a more cost-effective 16nm FinFET Compact Technology (16FFC). This process maximizes die cost scaling by simultaneously incorporating optical shrink and process simplification”と説明がなされている。

プロセス構成をやや簡単化するとともに、Optical Shrinkをかけて若干エリアサイズを小型化した、低コスト版の16nm FinFETプロセスである。

さてこれに続き、今年3月にTSMCがアナウンスしたのが12FFCである。これは、プロセスの物理的なパラメーターそのものは16FFCそのままである。もともと16FF+→16FFCの際にOptical Shrinkを実施しているが、これはたかだか数%という比率でしかないらしい。

つまりトランジスタのサイズそのものは、ほとんど16FF+と違いがない。例えば縦横1%縮小しても面積比では2%の縮小、寸法を5%縮められれば面積で1割削減になるため効果的ではあるのだが、一方でFinFETの世代では寸法をいじると急激に物理特性が変わってしまうので、いじるといっても影響のない範囲にとどめる場合、そんなに大きく変更はできないことになる。

しかも16FF+→16FFNで一度Optical Shrinkを行なっているので、さらなる縮小はかなり厳しい。実際には少しだけ余分にShrinkの度合いが増えているらしいが、ほとんど違わないそうだ。

ところが12FFCでは、16FFCと比較して9~12%の面積削減と15%の消費電力削減が可能、というのがTSMCの説明である。これは、スタンダードセルを6トラックにしたことで実現した。

スタンダードセルのサイズを縮小して小型化と省電力化、というのはかつてAMDがCarrizoでやった方法である。Carrizoの場合は12トラックのセルを9/7.5トラックで再設計しなおすことで面積を30%削り、消費電力を下げることにも成功したが、その代わり性能が上がらなくなっている。

この「性能が上がらない」は12FFCにも言えることで、したがって12FFCはメインストリーム向けのモバイルSoC向け、という位置づけになっていた。

ということで話を12FFNに戻す。こちらは端的に言えば16FF+に6トラックのスタンダードセルを適用した構造になっている。一応こちらにもOptical Shrinkをかけてはいるが、性能を犠牲にしないために、あまり大きく寸法をいじれなかったようで、結果トランジスタの寸法は16FFCよりも大きいらしい。つまり、サイズ縮小の効果は主にスタンダードセルに6トラックのものを利用したことに起因する。

その効果はあったのか?といわれれば、おそらくあったのだろう、という答えになる。Tesla V100のホワイトペーパーによれば、以下のようになっている。

| 各コアのスペック | ||||||

|---|---|---|---|---|---|---|

| コア名 | GP100 | GV100 | ||||

| アーキテクチャー | Pascal | Volta | ||||

| ダイサイズ(mm2) | 610 | 815 | ||||

| トランジスタ数 | 153億 | 211億 | ||||

| SM数 | 60 | 80 | ||||

ここから以下のように算出できる。

| ダイサイズの算出 | ||||||

|---|---|---|---|---|---|---|

| コア名 | GP100 | GV100 | ||||

| SMあたりのダイサイズ | 10.17mm2 | 10.19mm2 | ||||

| 1億トランジスタ当たりのダイサイズ | 3.986mm2 | 3.863mm2 | ||||

1億トランジスタあたりのダイサイズは微減、というあたりだがSMあたりのダイサイズは微増である。ただ実際にはVolta世代ではSMの中にTensor Coreと呼ばれるテンソル演算用のユニットが追加されている。

さらに共有メモリーサイズも若干増やされており、この増分を吸収してほぼPascalと同等のエリアサイズを実現するには、12FFNの採用が必須だった、ということだと思われる。逆に言えば、12FFNを使ってもそう大きくエリアが削減できるわけではない、ということでもある。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 - この連載の一覧へ