前回はSUPRENUMを解説したが、このSUPRENUMと期間をオーバーラップさせながら、別の超並列システムの開発がヨーロッパで行なわれていた。

この開発はEUのESPRIT(European Strategic Program for Research and Development in Information Technology:欧州情報技術研究開発戦略計画)という共同開発プロジェクトが主導していたものだ。

名前の通りこれは特定の国ではなく、EUそのものの共同研究プロジェクトであり、プロジェクトそのものは1983年に発足、1998年にはIST計画(Information Society Technology)に吸収される。

ISTはその後2007年にICT(Information and Communication Technology)に名前を変えて、現在も活発に作業を行なっているのだが、こちらの話は置いておく。

SUPRENUM-1の影響を多大に受けた

GENESIS

ESPRITが1989年から1992年の3年間のプロジェクトとして開発したのが、GENESISである。時期的には、すでにSUPRENUM-1の1号機が稼動している状態であり、ここでさまざまなソフトウェアの移植や性能評価などが行なわれていた状態である。

それもあって、GENESISのアーキテクチャーや実装にはSUPRENUM-1の影響が大きい。というよりプロジェクトの進行そのものにもSUPRENUMがかなり影響していた。

SUPRENUM-1

GENESISの3年間の開発プロジェクトでは、初年度にアーキテクチャー設計、2年目にハードウェアとソフトウェア、3年目はソフトウェアのみ(ハードウェア開発は一切なし)というなかなか迅速なものだったが、初年度の開発に関する管理請負業者(Managing Contractor)はなんとSUPRENUM GmbHである。連載330回でも触れた、SUPRENUMの製造・販売を目的とした会社である。

当たり前の話だが、新規に超並列システムの開発をゼロから始めるとなると、非常に多用多種の決めごとや契約、行なうべき作業が山積みとなる。幸いにもSUPRENUM GmbHはSUPRENUM-1の開発でこうしたことを一通り経験しているため、確かに最適である。

もっともSUPRENUM GmbHが請け負ったのは初年度だけで、2年目以降はGENESISのプロジェクトリーダーを務めていたUlrich Trottenberg博士が設立したPallas GmbHが契約を引き継いだ。

正確には、SUPRENUMのプロジェクトで開発されたさまざまなソフトウェアをPallas GmbHが引き継ぎ、これをGENESISに移植する作業を行なったことになる。

特にSUPRENUMで開発されていた、PARMACSと呼ばれる超並列環境におけるメッセージ伝達機構(超並列を構成するノード間で同期やデータ転送を行なうための仕組み)を移植可能なものに変更し、これをGENESIS上で動かすという作業に関し、Pallas GmbHは大きな役割を果たしたようだ。このあたりが、GENESISがSUPRENUM-1の後継と言われる所以でもある。

さてそのGENESISである。“The Architecture of the European MIMD Supercomputer GENESIS”という論文によれば、GENESISはCRAY-Y MPあるいはCRAY-2に匹敵するスーパーコンピューターを、超並列を利用して1MFLOPSあたり200ドル以下の価格で構築することにあった。

同論文の中で、製品カテゴリーを3つに分けているが、GENESISはスーパーコンピューターの市場を狙うシステムとされた。

| システムタイプ | 性能レンジ | 構成 |

|---|---|---|

| Super Workstation | 0.1~0.4GFLOPS | 1~4プロセッサー・1ボード・タワーケース |

| Super CAD System | 0.8~6.4GFLOPS | 最大16ノードのクラスター・キャビネット |

| Super Computer | 100~400GFLOPS | 1024ノード |

もっとも、100GFLOPSを1024ノードとするとノードあたり100MFLOPS、400GFLOPSだと400MFLOPSがそれぞれ必要になる。SUPRENUMはノードあたり20MFLOPSだったので、5~20倍の性能引き上げが必要になる。

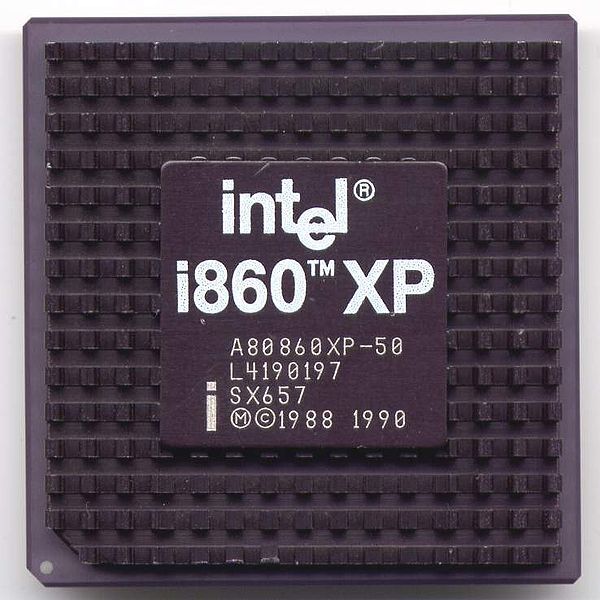

そこでGENESISではインテルのi860とその後継のi870に目をつけた。ちなみにi870というのは当時「予想されていた」名称で実際の製品名ではない。Intel i860は連載116回で取り上げたRISCプロセッサーで、当初リリースされたN10コアのi860XRは25/33MHz動作であった。FPUは同時に2命令を実行できるので、33MHz動作なら66MFLOPSとなり、もう一息である。

i860の後継であるN11コアは40/50MHz動作になってi860XPとしてリリースされた。i860XPを論文の中ではi870と称していたのだが、これを利用すれば50MHzで理論性能は100MFLOPSなので、1024ノードであれば100GFLOPSを越えることになる。

→次のページヘ続く (SUPERNUMを変形させたような構成)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ