FijiはTSMCの28nmプロセス?

チラ見せチップからダイサイズを試算

では、いよいよ肝心のFijiの話である。今回の説明会ではFijiチップそのものの実物展示はされなかった。会場では説明会の後でクローズアップ撮影の機会もあったようだが、WebCastではCGイメージしか示されなかった。

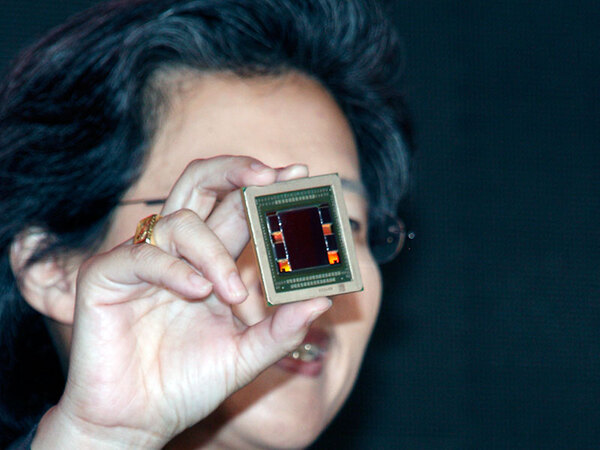

ただこれに先立つ6月3日に台湾で開催された第6世代APUの発表会で、社長兼CEOのLisa Su氏がFijiのチップをチラ見せしたのだが、この時の写真からある程度ダイサイズの推察が可能である。

というのは、SK HynixがHBMのダイサイズは5×7mmであると公開しているからで、あとは写真から寸法を推定可能である。筆者が試算したところ、GPUのダイサイズはおおむね22×26mmの572mm2になるであろう。

これはGeForce GTX TITAN Xなどに使われるGM200コアの600mm2にはおよばないが、従来のRadeon R9 290Xなどに使われてきたTahitiコアの438mm2の3割増しになる。ここから推定されるのは、TSMCの28nmプロセスを使っていると考えられることだ。

2014年7月にAMDが開催した投資家向けの決算発表の際に、当時はまだ上級副社長兼COOだったSu氏は「2015年中に20nmプロセスで製造したGPUを投入する」旨を明らかにしている。

これに基づき筆者はFijiを20nmプロセスで製造するとこれまで書いてきたのだが、20nmだとすると明らかにつじつまが合わない。

TSMCの20nmプロセスは、古くはNVIDIAのGM104のキャンセルや、最近ではSnapDragon 810搭載スマートフォンの異常発熱などでいろいろと話題である。

動作周波数をそれほど上げずに使えばトランジスタ密度を大きく上げられるため、トータルでの性能を上げやすい。その一番良い例がFPGAで、XilinxのUltrascaleシリーズやAlteraのArria 10シリーズは順調に出荷されている。

筆者はAMDもこれと同じ方法論を取るのかと考えていた。具体的に言えば、シェーダ数を増やす一方で、動作周波数を落とすという方式だ。

ただし20nmでは、同じダイサイズでトランジスタ数を最大90%増やせるため、現実問題としてダイサイズはHawaiiから増える必然性はほとんどない。逆に言えば、ダイサイズを3割も増やすと、シェーダー数はおよそ2.5倍になる。さすがにこれは多すぎるだろう。

また、20nmプロセスはまだそれほど熟成が進んでいないため、いきなり50mm2を超えるダイを製造するのは歩留まりの観点からはかなり危険なレベルである。

そう考えると、Fijiは昨年の公約とは裏腹に、28nmプロセスを使って製造されたものと考えるほうがつじつまが合う。公約はどうするんだろう? という話を別にすると、アーキテクチャーをGCNのまま維持するなら28nmのままの方が作りやすいうえ、歩留まりも上げやすいだろう。

シェーダー数は4096と発表されており、コンピュートユニット数は64にも達する。Hawaiiがシェーダー数2816なので45%ほどの増加である。

メモリー帯域は384GB/秒から512GB/秒で33%ほどの増加になるので、ROPはこのメモリー帯域増加にあわせて96基程度になっていると想像されるが、実はまだHBM AccessのGranularity(粒度)がはっきりしない。

GDDR5の場合は512bit幅を32bit×16と分割、それぞれのメモリーコントローラーが独立で動く形で、1つのメモリーコントローラーに4つのROPが割り当てられる計算だったが、このあたりがHBMで共通かどうかはよくわからない。

ROP数が96という試算はあくまでGDDR5と同程度のGranularityが維持されていることを前提とした数字である。

(→次ページヘ続く 「「Radeon R9 Fury」シリーズのロードマップ」)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ