ややこしいUSBの転送速度

前述のCOMPUTEXにおけるUSB-IFの資料では、USB 3.0が5Gbpsでの通信ができることになっているが、これは正確ではない。正しくは5GT/sec( (5 GigaTransfers per Second)である。USB 3.0はPCI Express Gen2とPHY(physical Layer)を共用した関係で、信号の速度そのものは5GHzになっている。

5GHzならば5Gbpsだと思われるかもしれないが、内部で8b/10bエンコードという信号処理方法を採用した関係で「8bit分のデータを送ると、10bit分のシンボルに変換される」ことになる。

シンボルそのものは5GHzの信号速度になるが、データとしては8割に相当する4GHz分の4Gbpsでの通信になる。このあたりが誤解を招きやすいので、PCI Expressではあえて4Gbps/5Gbpsといった表記ではなく、5GT/sec(5G Transfer/second)という表記にしている。

これをUSB-IFで5Gbpsとしてしまった理由はおおよそ見当がつく。PCI Expressはある意味技術者向けの規格だから正確さが優先されるが、USBはコンシューマー機器に広く使われるものであり、正確さよりもわかりやすさが優先されるということだろう。以上のことから、USB 3.0では実効データ転送速度が4Gbps=500MB/秒になっていた。

ではUSB 3.1ではこれがどうなったかというと、以下のようにそれぞれ変更した。

- 信号転送速度を5GHz→10GHzに

- エンコードを8b10b→128b132bに

この結果、通信速度は10G×128÷132=9.6969Gbps≒1.21212GB/秒で、USB 3.0の2.4倍もの転送速度に向上した計算になる。おもしろいのは、SuperSpeedPlusのスペックが、PCI Express 3.0とまったく互換性がないことだ。PCI Express 3.0では以下のように変更している。

- 信号転送速度を5GHz→8GHzに

- エンコードを8b10b→128b130bに

通信速度が8G×128÷130=7.877Gbps≒0.985GB/秒となっている。ちょうど2倍、という意味ではPCI Express 3.0の方が近く、USB 3.1はこれを上回る仕様になっている。

また実装については、USB 3.1デバイスは必ずUSB 3.0デバイスとの互換性を取ることが必須とされている。ただ信号速度もエンコード方式も違うから、基本的には別のデバイスということになる。

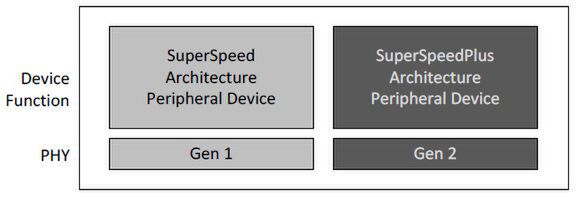

そこで内部的には下図のように、見かけ上は1つのデバイスであっても、内部的にはUSB 3.0で動作するデバイスとUSB 3.1で動作するデバイスの2つが入っており、SuperSpeedPlusで動作できるか否かで、どちらのデバイスが動くかが決まる構造になる。

もっと言ってしまえば、元々USB 3.0ではUSB 2.0までとの互換性を取ることが必須になっており、3.0と2.0では信号線まで違うから、こちらも物理層が違っているうえ論理層も異なっている。それらとの互換性を保つUSB 3.1デバイスの動作をまとめると、以下のようになる。

- EnhancedSuperSpeedの論理層+SuperSpeedPlusの物理層

- EnhancedSuperSpeedの論理層+SuperSpeedの物理層

- USB 1.1/2.0の論理層+USB 1.1/2.0の物理層

このようにUSB 3.1デバイスは、上記3種類の動作を求められるという厄介な状況になっている。

既存のUSBとの互換性

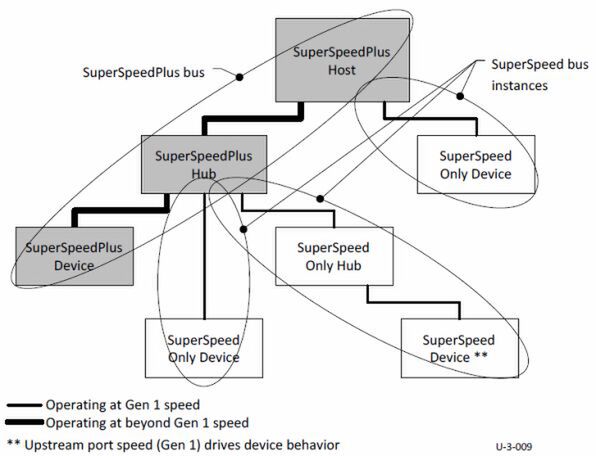

ケーブル及びコネクターは、既存のUSB 3.0のケーブル/コネクターと同一の仕様になっており、きちんと互換性が取れている。ただしハブなどを介しての接続は、従来同様に「上流の速度で下流の速度が決まる」という原則が貫かれる。

上の画像は、USB 3.1のホストにUSB 3.1のハブとUSB 3.0のハブ、USB 3.1/USB 3.0のデバイスが混在するというケースだが、要するにホストがUSB 3.1対応であっても、途中にUSB 3.0ハブが入ったらそのハブの下は全部USB 3.0扱いになり、USB 2.0ハブが入ればUSB 2.0扱いになるという仕様である。

一方ソフトウェアの面から見ると、ホストコントローラーのデバイスドライバを除くと今のところ変更点はないので、様々なクラスドライバーやフィルタドライバー、あるいはアプリケーションがそのまま利用できる「はず」である。

わざわざ「はず」とつけたのは、まだ仕様が固まっただけで実際のデバイスでのテストが行なわれていないからで、このあたりの互換性の確認は今後の課題になるだろう。

以上のことから、EnhancedSuperSpeedに関して言えば、純粋に速度が上がった「だけ」ということになる。細かいところでは、速度向上に応じて当然ノイズなどがよりシビアな問題になるわけだが、それはメーカーが考えるべきことでありユーザーには縁がないだろう。

「EnhancedSuperSpeedに関して言えば」というのは、USB 3.1にはあと3つ仕様があるからだ。1つ目は2011年6月にリビジョン1.0が、2012年5月にリビジョン1.1が出たOn-The-Go and Embedded Host Supplement to the USB Revision 3.0 Specification。

2つ目は、昨年6月にリビジョン1.0/バージョン1.0がリリースされ、今年6月にリビジョン1.0/バージョン1.2まで上がったUSB Power Delivery Specification。

3つ目は昨年5月にリビジョン1.0が出て、今年2月にリビジョン1.1となったInter-Chip Supplement to USB Reivison 3.0 Specificationである。

この3つの仕様書は独立した形でリリースされているが、USB 3.1はこれら3つの仕様にも準拠することが求められているためだ。そこで、この3つについても簡単に説明しておく。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ