ロードマップのアップデートが一段落したので、久しぶりにチップセット黒歴史をお届けしよう。今回のテーマはGreencreekことIntel 5000Xチップセットである。

Intel 5000Xチップセット

デスクトップ用というよりはワークステーション/サーバー向けチップセットに分類されるものだ。それでもごくわずかながら個人ユーザーで使われた方もいたようで、後継となるSeaburgはSkullTrailプラットフォームという超ハイエンド向けで採用されているため、デスクトップともまるっきり無縁ではないので説明していきたい。

FSBを2つ搭載する

Intel 5000シリーズ

Intel 5000Xの元になったIntel 5000シリーズというチップセットが登場したのは2006年5月である。このIntel 5000シリーズは、Blackfordというコード名で開発されたものだ。経緯は連載38回で説明したが、おさらいしておこう。

2006年当時、インテルはAMDに比べてネイティブのマルチコアCPUの導入がやや遅れていた。元々AMDは、最初のOpteronとなるSledgeHammerコアの時から、コアそのものは1つながら、内蔵するノースブリッジ部はデュアルコア構成を相当した作りになっており、2005年に投入したK8 Revision E(Egypt/Italy/Denmark)コアではプロセスの微細化によりネイティブでデュアルコア化する。

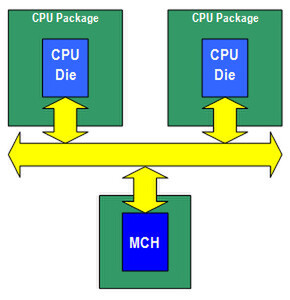

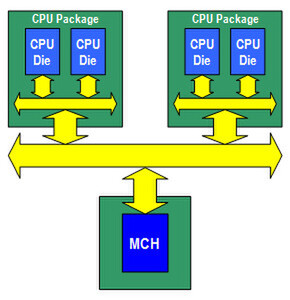

対するインテルは、2006年に投入したDempseyベースのXeonでやっとデュアルコア化を実現するが、このDempseyはPentium Dと同じく1つのパッケージに2つのダイを搭載し、間をFSBで繋いだ構成になっていた。

これのなにが問題だったかというと、電気的にはCPUのパッケージ1個で2P相当になるから、デュアルプロセッサー構成というのは実質的に4P構成になり、FSBの速度を下げないと安定動作しないことになった。

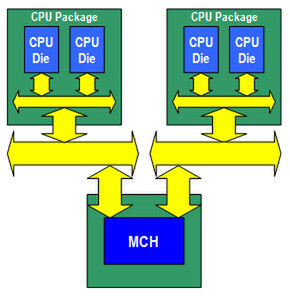

またXeon MP向け、つまりクワッドプロセッサー構成だと電気的には8P構成になり、これはインテルのFSBではサポートできないことになった。これに対応するため、FSBを2つ搭載したのがBlackfordシリーズのチップセットである。

FSBを2つに分ければ、例えばデュアルプロセッサー構成だと1本のFSBあたり2Pになるし、クワッドプロセッサーでも1本のFSBあたり4Pだから、これは従来と構成的に変わらないことになる。

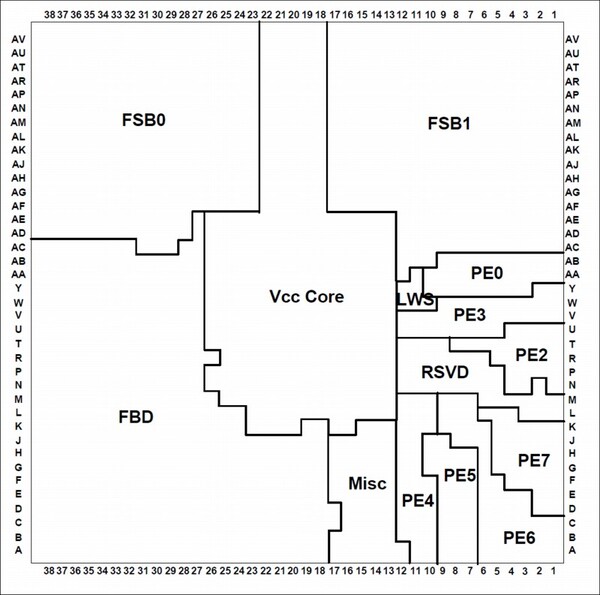

もっとも、これはあまりに力技といえば力技な解決法で、チップセットのボール数は1432個にも達しており、多層基板(安定して利用するには10層以上が必要だった)と相まってかなり搭載マザーボードは高価になったが、サーバー/ワークステーション向けだからこれは許容されたとも言える。

またクワッドプロセッサーに関しては、FSBを分割してもまだFSB1本あたり4Pとなり速度を上げにくいため、結局後継となるIntel 7300チップセットまで見送りになってしまった(こちらはFSBが4本出る)。

ちなみにこのIntel 5000シリーズは3製品がラインナップされており、以下のようになっている。

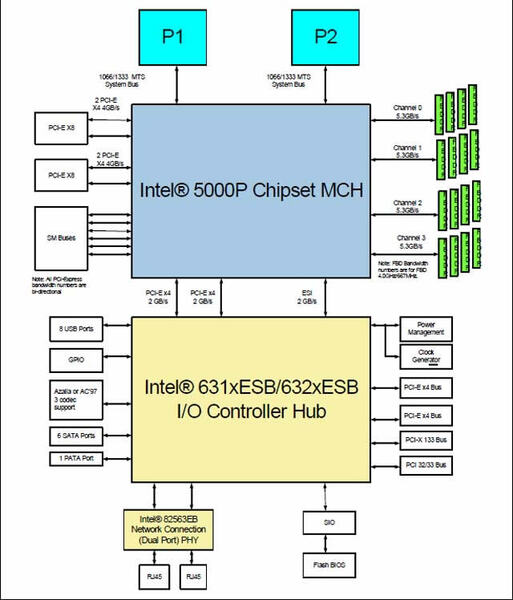

- Intel 5000P:ハイエンドサーバー向けの全部入り構成。FB-DIMMを4ch搭載し、PCI Express x4レーンを4本搭載する。またメモリーチャンネルのミラーリング機能も搭載

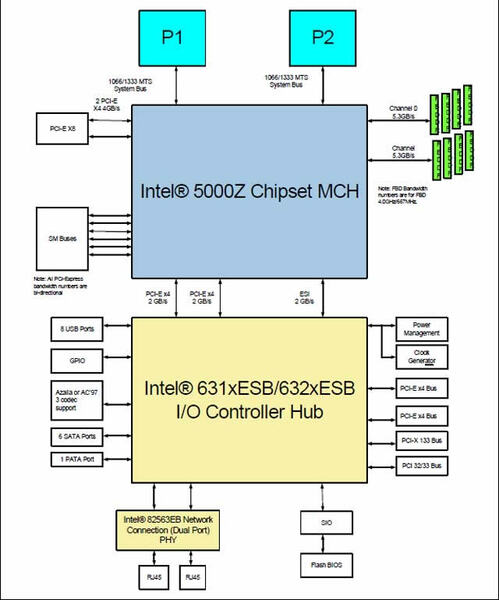

- Intel 5000Z:Intel 5000Pの廉価版。メインストリームサーバー向け。FB-DIMMは2chに削減され、PCIe x8レーンも1本に減らされた。メモリーチャンネルのミラーリング機能も削減。

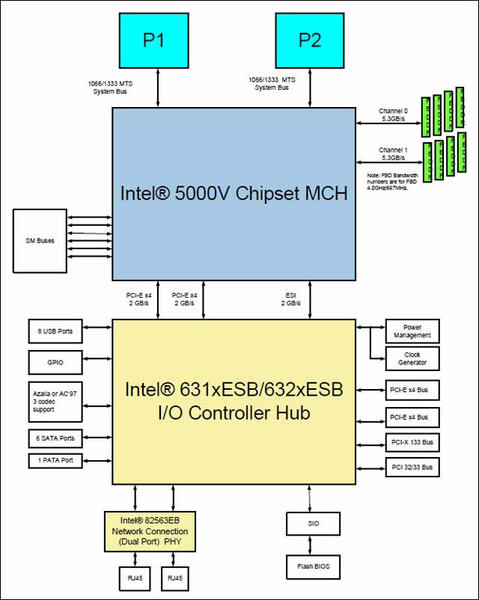

- Intel 5000V:さらに安価なバリュー向け構成。PCIeを完全に削減。ただそれ以外はIntel 5000Zとまったく変わらない。

なぜかIntel 5000Vのみコード名がBlackford-VSだが(Intel 5000ZはBlackford)、内部はまったく同じであり、パッケージもPCI Expressや未使用のFB-DIMMのものがReservedになっている以外は違いがない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ