仮想化関連の補足規格も用意

ただし普及は進まず

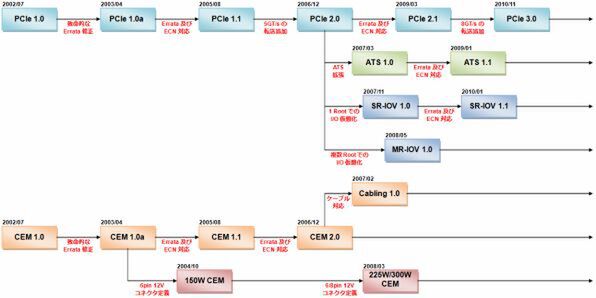

ここまでがBase Specificationを中心としたロードマップであるが、これを補足するものとして、2007年3月に「Address Translation Services 1.0 specification」(ATS 1.0)がリリースされた。これはAMDなら「IOMMU」、インテルなら「VT-d」として実装されている、仮想環境でI/Oデバイスのアクセスを高速化するための技法である。

これをもう一歩進めて、デバイス自体を仮想化に対応させるための仕様が、2007年11月に登場した「Single Root I/O Virtualization and Sharing 1.0 Specification」(SR-IOV 1.0)である。こちらはひとつのマシン上で複数の仮想マシンが動作して、これがそれぞれI/Oアクセスするという環境を想定した規格で、各デバイス自身が仮想化をサポートして、複数の仮想マシンと通信するための仕様を定めたものである。

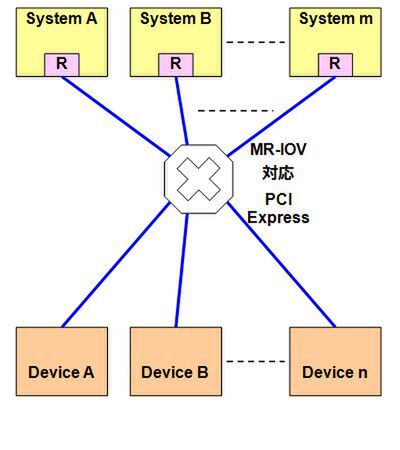

2008年5月にリリースされた「Multi-Root I/O Virtualization and Sharing 1.0 Specification」(MR-IOV) は、さらにこれを進化させた規格である。MR-IOVは図6のように複数のシステム(例えばブレードサーバー)とデバイスを接続して、デバイスをシステム間で共用しようというものである。

ATSはWindows 7のVirtual PCなどで効果が出るので、個人ユーザーでも恩恵がある。一方SR-IOVは、デバイスとデバイスドライバーが仮想化に対応する必要があるし、MR-IOVではさらにPCI Expressスイッチも専用のものが必要となる。用途としては完全にハイエンドシステム向けであり、そんな理由もあってあまり普及しているとは言い難い。

カードにケーブル接続、電力供給も規格化

最後に、冒頭で名前だけ出たCEMについても触れておこう。CEMも基本的にはBase Specificationに合わせてRevisionを上げているが、現時点での最終版は「CEM 2.0」止まりとなっている。PCI Expressでは互換性を重視したため、電気的特性に関してはPCIよりもさらに差が少なく、純粋にコネクタ類の機械的形状に関する訂正などが主な変更点となっている。そのため8GT/秒のRevision 3.0でも、CEM 2.0のまま利用できるということになっている。

このCEM 2.0を元に、2007年2月にはケーブル接続のための「PCI Express External Cabling 1.0 Specification」が策定されている。実はこのCablingは、Revision 1.0の時点から仕様策定が始まっていた。しかし、その時点で「次のBase Specificationが5GT/秒になる」ことがほぼ見えていたので、当初から5GT/秒をターゲットに仕様策定が進められていた。その結果として、CEM 2.0の完成を待ってCabling 1.0が策定されたわけだ。

これに続く8GT/秒のケーブル接続に関しては、現時点でもまだ作業中ということになっている。そもそも8GT/秒対応のCablingの仕様が、出るかどうかを含めて未定である。

CEMに関してはもうひとつ、大消費電力向けの拡張仕様がある。PCI Express自身はレーンから3.3V/3Aと12V/5.5Aの合計75Wが最大供給電力となっている。もっともこれはx16の場合で、x1では12V/0.5Aで合計10W、x4/x8では12V/2.1Aで合計25Wに制限されている。

実際にはこの75Wでは足りない拡張カードがあるということで、2004年10月に追加策定されたのが「PCI Express x16 Graphics 150W-ATX Specification 1.0」である。これにより、追加の6ピンコネクター経由でさらに75Wを供給し、合計150Wまでが利用可能になった。ところがこれでもまだ足りないということで、2008年3月に策定されたのが「PCI Express 225W/300W High Power Card Electromechanical Specification 1.0」である。こちらではさらに8ピンの電源コネクターも定義されている。

- 6ピン×1 最大150W

- 6ピン×2 最大225W

- 6ピン+8ピン 最大300W

ちなみに、仕様には6ピン×3とか8ピン×2などはなく、これはベンダーが勝手に実装した独自仕様である。このあたりの独自仕様について以前にPCI-SIGの議長に尋ねたところ、「そうしたハイエンドは非常に限られた製品のみで、通常は300Wのみで足りる。仕様をさらに拡張するつもりもないし、限られた製品が独自拡張をしても、それが一般的になるわけではないから特にあれこれ言うつもりはない」という返事だった。そんなわけで、こちらも後継規格が登場する可能性は今のところ低そうである。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ