今回は「PCI」の後継となる、現在の主流規格「PCI Express」について解説したい。

PCIと同様に

インテルから生まれたPCI Express

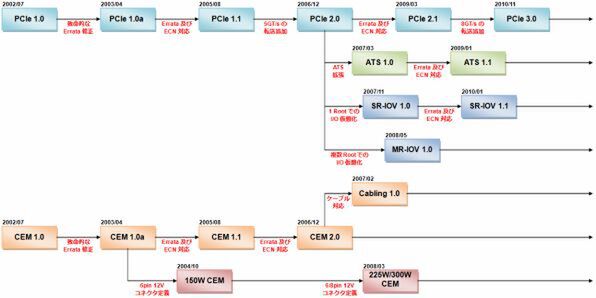

PCI ExpressもPCIと同様に、当初はインテルが「3GIO」(3rd Generation I/O)というコード名で開発していた規格だ。ある程度それに目鼻がついたところで、標準化団体「PCI-SIG」に標準化作業が移管された。最終的にこの規格がPCI Expressと命名されて、2002年7月に「Base Specification Revision 1.0」がリリースされる。

Base Specificationというのは、PCI Expressの「基本」となる仕様書である。あえてこういう書き方をするのは、ほかにも仕様書がいろいろあるからだ。Base Specification 1.0と同時に「CEM (Card Electromechanical) Specification 1.0」という仕様がリリースされている。

CEMはその名のとおり、PCI Expressを使った拡張カードの物理/機械的な仕様と、そこに流れる信号の電気的な仕様を定めたものだ。逆に言えば、Base Specificationに電気的仕様はあまり入っていない(基本的な項目のみ)。むしろ電気的仕様の上位になる信号層や、論理層/トランザクション層の仕様が主となっている。

追加された仕様書はほかにもあり、「Cabling」とか「Express Card」「PCI Express Mini Card」(ロードマップ図では省略)なども含まれている。またこれもロードマップ図では省略したが、「Compliance/Test」に関する仕様も、Base Specificationには含まれていない。これは、当初からPCI Expressが非常に広い範囲で利用されることを想定しており、「Base Specificationに全部盛り込んでしまうと煩雑に改定が必要になる」といった問題に備えてのことである。

そのPCI Expressだが、基本的には以下の3点が主な特徴になる。

- ① Point to Pointで全二重通信

- ② ディファレンシャル伝送

- ③ Embedded Clockによるシリアルバス

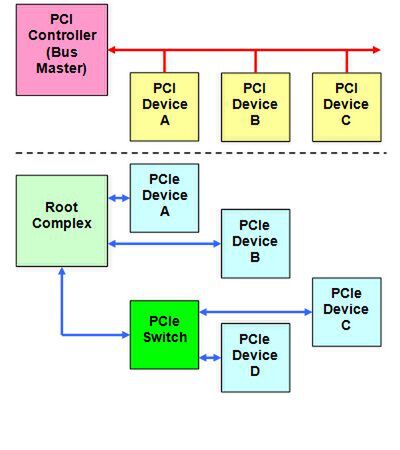

まず「全二重通信」だが、従来のPCIやPCI-X/AGPは図1上側のように、1本のバスにすべてのデバイスがぶら下がっている。対するPCI Expressでは、図1下側のように大本のコントローラー(Root Complex)と各デバイスが、すべて独立した配線で接続される。これでも拡張性が足りない場合はPCI Expressスイッチを介して複数のデバイスをつなげる仕組みだ。

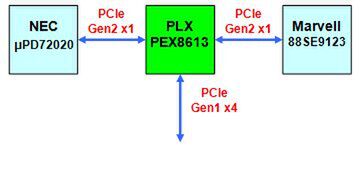

このPCI Expressスイッチを使った有名な例が、ASUSTeKのコンボインターフェースカード「U3S6」である。U3S6は図2のような構造になっており、米PLX Technologyの「PEX8613」というPCI Express Gen2(2.x世代)の4レーン×3のスイッチの先に、MarvellのSATAコントローラーとNECのUSB 3.0コントローラーをぶら下げている。レーンの数が少ない場合、こうしたスイッチを使うことで自由にデバイス数を増やせるため、PCIなどと比較しても利用できるデバイス数に遜色がない、というのが特徴である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 - この連載の一覧へ