今回は「PCI」の後継となる、現在の主流規格「PCI Express」について解説したい。

PCIと同様に

インテルから生まれたPCI Express

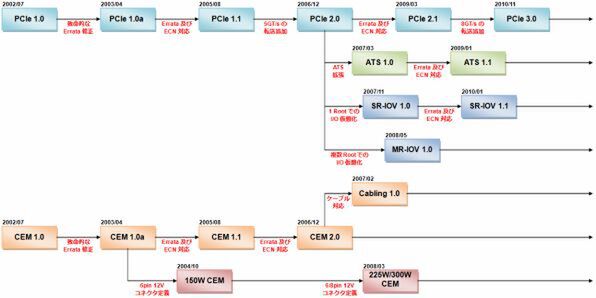

PCI ExpressもPCIと同様に、当初はインテルが「3GIO」(3rd Generation I/O)というコード名で開発していた規格だ。ある程度それに目鼻がついたところで、標準化団体「PCI-SIG」に標準化作業が移管された。最終的にこの規格がPCI Expressと命名されて、2002年7月に「Base Specification Revision 1.0」がリリースされる。

Base Specificationというのは、PCI Expressの「基本」となる仕様書である。あえてこういう書き方をするのは、ほかにも仕様書がいろいろあるからだ。Base Specification 1.0と同時に「CEM (Card Electromechanical) Specification 1.0」という仕様がリリースされている。

CEMはその名のとおり、PCI Expressを使った拡張カードの物理/機械的な仕様と、そこに流れる信号の電気的な仕様を定めたものだ。逆に言えば、Base Specificationに電気的仕様はあまり入っていない(基本的な項目のみ)。むしろ電気的仕様の上位になる信号層や、論理層/トランザクション層の仕様が主となっている。

追加された仕様書はほかにもあり、「Cabling」とか「Express Card」「PCI Express Mini Card」(ロードマップ図では省略)なども含まれている。またこれもロードマップ図では省略したが、「Compliance/Test」に関する仕様も、Base Specificationには含まれていない。これは、当初からPCI Expressが非常に広い範囲で利用されることを想定しており、「Base Specificationに全部盛り込んでしまうと煩雑に改定が必要になる」といった問題に備えてのことである。

そのPCI Expressだが、基本的には以下の3点が主な特徴になる。

- ① Point to Pointで全二重通信

- ② ディファレンシャル伝送

- ③ Embedded Clockによるシリアルバス

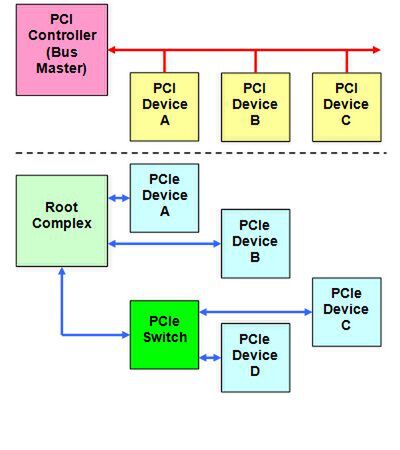

まず「全二重通信」だが、従来のPCIやPCI-X/AGPは図1上側のように、1本のバスにすべてのデバイスがぶら下がっている。対するPCI Expressでは、図1下側のように大本のコントローラー(Root Complex)と各デバイスが、すべて独立した配線で接続される。これでも拡張性が足りない場合はPCI Expressスイッチを介して複数のデバイスをつなげる仕組みだ。

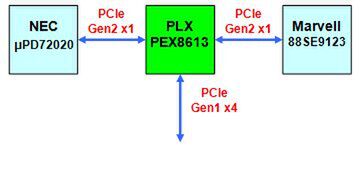

このPCI Expressスイッチを使った有名な例が、ASUSTeKのコンボインターフェースカード「U3S6」である。U3S6は図2のような構造になっており、米PLX Technologyの「PEX8613」というPCI Express Gen2(2.x世代)の4レーン×3のスイッチの先に、MarvellのSATAコントローラーとNECのUSB 3.0コントローラーをぶら下げている。レーンの数が少ない場合、こうしたスイッチを使うことで自由にデバイス数を増やせるため、PCIなどと比較しても利用できるデバイス数に遜色がない、というのが特徴である。

この連載の記事

-

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 - この連載の一覧へ