パイプラインハザード対策には、分岐予測やパーシャルフラッシュ

これを補うための方策として広く利用されているのが、分岐予測機構である。パイプラインハザードは要するに、「間違った方向の命令をデコードするから発生する」とも言えるわけで、正しく命令をデコードすればこうした事態は防げる。そこで、デコードの際に分岐命令を発見したら、「次にどちらの方向に分岐するか」をきちんと判断して次の命令を決める仕組みが、今のCPUには搭載されている。

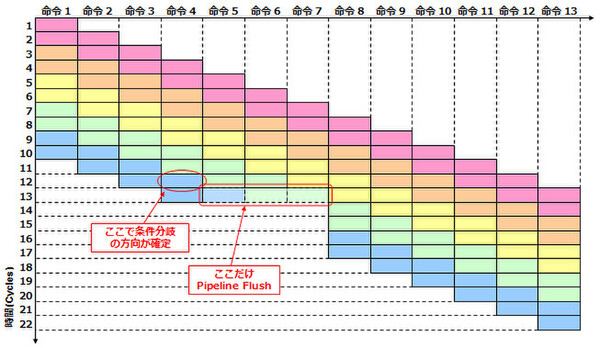

また「パーシャルフラッシュ」と呼ばれる仕組みを搭載しているものもある。図4では分岐ミスが発生した場合、パイプライン全体をフラッシュしていた。しかし図4の場合、間違っているのは命令5~7までの処理で、命令8以降はそのまま継続しても問題ない。そこで、命令5~7を処理しているステージのみフラッシュすることで、パイプラインハザード時のペナルティを軽減しようというものだ。

実際図5の場合、ペナルティは3サイクル分で済んでいる。もっともこの機構は単純なパイプラインでは実装しやすいが、さまざまなテクニックを駆使している昨今のパイプラインでは、機構的に複雑になりすぎてしまうため実装されないこともある。

ほかにも、分岐ミスが発生することを前提に、発生した場合のペナルティを軽減する仕組みがある。Decodeで分岐を確認した場合、その分岐先を2つとも内部のテーブルに格納しておくというものだ。これにより分岐ミスが発生した場合も、ただちに次のデコードを開始できる。

もっと積極的な方法としては、「投機実行」という仕組みを実装しているCPUもある。例えばインテルのItaniumだ。図3では、命令4のどちらか片方だけを実行するから、外れた場合にペナルティが大きい。それならば、命令4の後に命令5/6/7と命令8/9/10の両方を同時に処理をしておき、命令4の結果が確定した時点で、間違った分岐の結果を捨てるという、Partial Flushをもっと積極的に行なうような仕組みだ。ただこれはCPUが複雑になりすぎることもあって、採用例はほとんどない。

パイプラインの問題とそれをカバーする技術をざっとおさらいしたところで、次回は別の高速化技法である「スーパースカラー」について紹介したい。

この連載の記事

-

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ -

第849回

PC

d-MatrixのAIプロセッサーCorsairはNVIDIA GB200に匹敵する性能を600Wの消費電力で実現 -

第848回

PC

消えたTofinoの残響 Intel IPU E2200がつなぐイーサネットの未来 - この連載の一覧へ