CPUの性能発揮を阻害する「パイプラインストール」

前回に続き、今回もCPUのパイプライン処理について解説する。前回の最後では、「パイプライン段数を無闇に増やしても問題」という話をした。理由のひとつは消費電力だが、これはまた別の話になるので、今回はもうひとつの理由である「パイプラインストール」と「パイプラインハザード」の方を取り上げてみたい。

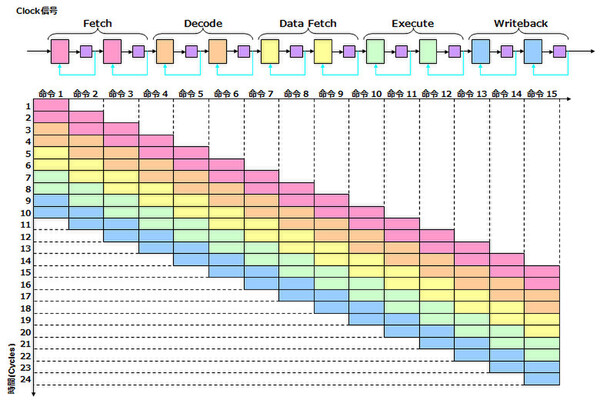

この2つは時々混同されることもあるが、基本的には別の要因で発生する問題であり、対応方法もちょっと異なる。まず前提として図1のようなケースを考えてみる。パイプライン段数は10段となっているため(昨今のx86プロセッサーから言えば短め)、例えば15個の命令を処理するのに要する時間は、合計24サイクルを要する計算だ。

まずパイプラインストールだが、これはパイプラインが「止まる」(Stall)することを示す。よくありがちなのは、Data Fetchだ。これは要するにデータを取り込む処理である。

- C=A+B

例えば、命令3が上の命令「AとBを加算して、Cに結果を入れる」を実行する場合、加算に先立ってAとBの値を確定しなければならない。この値の格納にはCPU内部のレジスターが割り当てられることが多く、この場合は遅れが出ない。通常なら、内部レジスターは1サイクルでアクセスできるためだ。

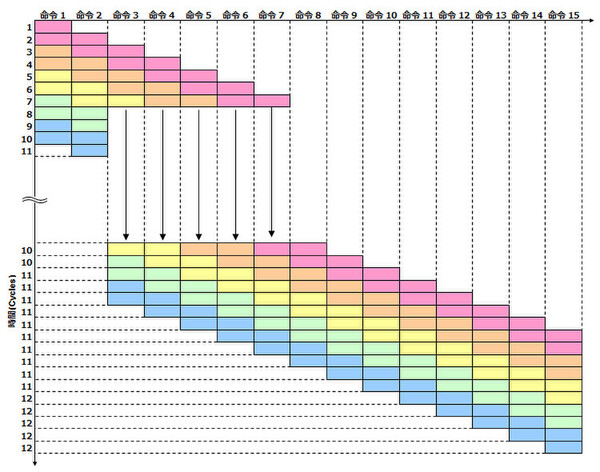

ところがレジスターの数は必ずしも多くないし、レジスターにすべてのデータが入っているとも限らない。どこかでメモリーにアクセスする必要がある。上の命令のケースでは、「Aはレジスターが使えるが、Bはメモリーから値を取得する必要がある」と想定しよう。するとどうなるか? というのが、次の図2である。

7クロック目までは、順調にパイプラインの各ステージが動作する。ところが、7クロック目のData Fetchステージ(図中の黄色部分)でメモリーアクセスが発生すると、パイプラインはそのデータをメモリーから読み込むまで、待機することになる。図1を見直してもらうとわかるが、パイプラインの場合は「あるステージが待機すると、それ以後のステージも全部待機せざるをえない」という欠点がある。そのため命令3以降の処理は全部、メモリーアクセスから帰ってくるまで待機することになる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ