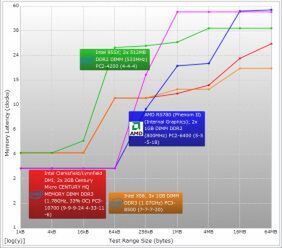

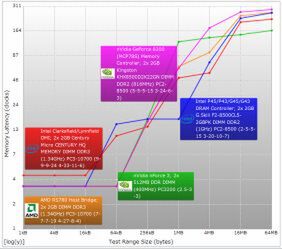

問題は「どの程度待たされるか」である。一例として、手元にあったCore i5-750(2.66GHz)を使って、総合ベンチマークソフト「Sandra 2010」のMemory Latencyテストを実行してみた。

左がシーケンシャルアクセスの場合で、1次キャッシュにヒットする範囲では3~4サイクル、2次キャッシュだと10~20サイクル程度で済むが、メモリーアクセスになると50サイクル以上必要になる。右はランダムアクセスのケースで、こちらではさらに酷くなっているのがわかる。特にメモリーアクセスでは、200サイクル以上要している。

つまり、何も工夫しないでメモリーアクセスが発生してしまうと、図2のようにただ漠然とパイプラインを止めて数百サイクル待機する、というばかげた状況に陥ることがわかる。このケースでは、15命令の処理に124サイクル必要とするわけで、図1の理想的な動作の、20%の性能しか出せないことになる。

メモリーとCPUの速度差を埋めるキャッシュの活用

これを避けるためにはどうするか? まず最初のアイディアが「キャッシュの利用」である。80286あたりの世代までは、CPUとメモリーの速度にそれほど大きな乖離がなかった。ところが80386世代の後半から、次第にCPUの速度がメモリーの速度を大幅に上回るようになる。そのためメモリーアクセスだけで済ませると、メモリー速度の遅さに足を引っ張られるようになってきた。

そこで、CPU側あるいはチップセット側にキャッシュメモリーを用意することで、スピードの差を埋めるという方策がとられるようになった。ただしキャッシュも万能ではなく、またダイサイズを低く抑えるという観点からも、そうそう大量のキャッシュは搭載しにくい。これを補うため、キャッシュに階層構造を設けたり、キャッシュ管理を工夫したり、キャッシュの構成自体を工夫したりとさまざまなテクニックが利用されるようになった。

また、キャッシュをいくら積んでも、そこに必要とされるデータが入っていないと意味がない。これを解決するために、「プリフェッチ」(データの先読み)と呼ばれる技法が広く使われている。より積極的にプリフェッチを実現するために、「ヘルパースレッド」「Victim Thread」などと呼ばれるマルチスレッド技法もある。もっともこちらは引き続き研究が続けられているようだが、これを最初に搭載する予定だったのが幻のインテルCPU「Tejas」とみられているだけに、その後もこれを積極的に利用した例は現れていない。

もっと積極的に、「そもそもデータをキャッシュなりレジスターに取り込むまで、パイプラインに命令を取り込まない」という、逆転の発想を実装したプロセッサーも存在しており(x86ではないが)、これは「ストールフリーパイプライン」などと呼ばれている。また別のアイディアには、「メモリーアクセスが発生してもパイプラインを止めない」という仕組みがある。これは「アウトオブオーダー」として実装されることになったが、これは別の回で説明することにしたい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ