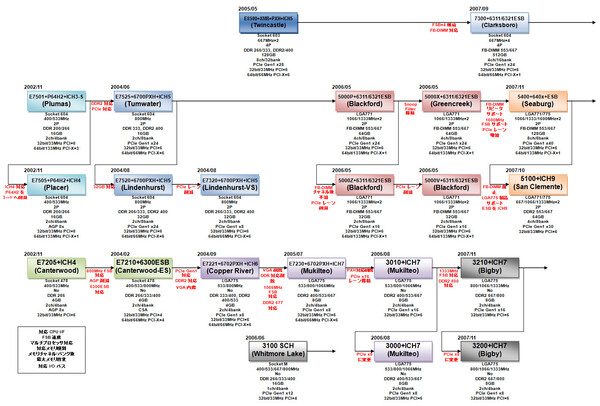

Intelチップセットの歴史 その8

FSB方式の限界に振り回されたXeon向けチップセット

2010年02月08日 12時00分更新

FSB方式の限界にぶち当たったXeonとチップセット

こんな具合に1プロセッサー向けチップセットはどんどん出てきた一方で、2プロセッサー向けチップセットは、2004年のE7525からしばらく、何も出ないままだった。というのも、FSB方式を踏襲したがゆえの問題にぶち当たったためである。

そもそもFSB方式の場合、1本のバスにチップセットとすべてのCPUがぶら下がっているから構造的には簡単な反面、高速化のためには信号波形の乱れや伝達遅延の問題が大きく影響してくるため、簡単ではなかった。実際、Pentium II XeonやPentium III Xeonの頃の、「100MHz FSBならば4プロセッサー構成が可能だが、133MHz FSBでは2プロセッサー構成に限られる」制限はこれが理由である。

しかも、Pentium 4以降に利用されたP4バスの場合、データレートが4倍になったため、この問題はさらに深刻になった。実際インテルは、Xeon MPシリーズの最初の製品である「Xeon MP 1.5/1.9/2GHz」を2002年11月に発表するが、これに対応したチップセットをインテル自身では提供できず、ServerWorks社の「ServerSet IV Grand Champion HE」(GC-HE)が唯一対応したチップセットとして出荷されるという有様だった。GC-HEにしても、対応できるFSBは400MHzまでで、それ以上では動作しなかったから、このあたりがShared Bus方式の限界というべきなのだろう。

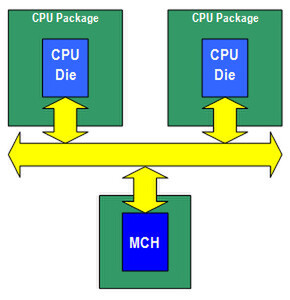

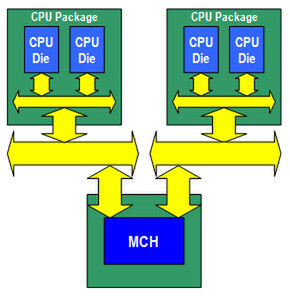

この限界は、意外な形で2プロセッサーサーバーにも影響することになった。というのも、Pentium Dと同じく2つのCPUダイをMCMの形で1パッケージに搭載した「デュアルコアXeon」が投入されたからだ。それまでは下の図1のように、ひとつのCPUパッケージにはひとつのCPUダイしか載っていなかったから、2つのCPUをつないだ場合でもバスにつながるのは合計3つ(CPU×2+MCH)のダイでしかなかった。

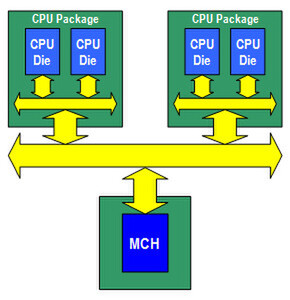

ところがデュアルコアXeonの場合、ひとつのCPUパッケージに2つのダイが搭載され、間が共有バスで接続されている。そのため2つのCPUパッケージを接続した場合、バスにつながるのは合計5つのダイになってしまう(図2)。この状態で問題なく動作させるためには、800MHzのFSBなどとんでもない話で、400MHzでも怪しくなる。が、これはそのまま激しい性能低下につながるわけで、到底許容できない。

そのため、1プロセッサーサーバーにデュアルコアXeonが投入された後も、長らく2プロセッサーサーバー向けには投入されなかった。しかしそのままでは競争力がなくなるため、本来Xeon MP向けに開発された「Paxville-MP」というネイティブデュアルコアCPU(ひとつのダイに2つのPentium 4コアを搭載した)製品を、2プロセッサー向けに転用した「Paxville-DP」を、「デュアルコアXeon 2.80GHz」として2005年10月に投入して間をつないだ。しかし、あくまでこれは急場しのぎだ。

複数FSBに対応して2プロセッサー構成を

可能にしたIntel 5000シリーズ

最終的には図3のように、MCHからFSBが2本出て、それぞれがひとつのCPUと接続するという形で2プロセッサー構成を可能にするという力技の解決が行なわれた。この2本のFSBが出てくる最初のチップセットが、2006年5月に発表された「Intel 5000」シリーズである。

この2006年5月というのは、CPUアーキテクチャーがPentium 4系の「NetBurstアーキテクチャー」から、「Coreマイクロ・アーキテクチャー」に変わったタイミングでもある。これに合わせてインテルは、チップセットの名前の付け方を変更。7000シリーズが4プロセッサー向け、5000シリーズが2プロセッサー向け、3000シリーズが1プロセッサー向けとなる。その最初の製品が「Intel 5000P/Z/V/X」となった。このうち、5000P/Z/Vはサーバー向け、5000Xがワークステーション向けとなっており、またメモリーに「FB-DIMM」を採用した最初のラインナップでもある。

ところで、5000Pと5000Xの最大の違いは、「Snoop Filter」を搭載するか否かである。詳しい説明は省くが、これはCPUごとのキャッシュ情報を確認するSnoop動作を最小限に抑えることで、FSBの利用効率を上げるという仕組みである。ただ最初の実装では、Snoop Filterのアクセスの方が遅くなり、むしろレイテンシが悪化するといった弊害もあったようで、必ずしも有効に機能したとはいえなかったようだ。

この連載の記事

-

第770回

PC

キーボードとマウスをつなぐDINおよびPS/2コネクター 消え去ったI/F史 -

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ - この連載の一覧へ