IPCの引き上げは難しい

シンプルな解決策がCPU数の増加

今回のテーマはマルチコアである。もともとコンピューターの世界では、CPUのコアをいっぱい並べるという技法は、非常に一般的であった。66回でも書いたが、CPUの処理性能は以下の式で表わされる。

- P=F×IPC

PがPerformance(処理性能)で、FがFrequency(動作周波数)、IPCは「Instructions Per Cycle」(1サイクルあたりの処理命令数)となる。Pを引き上げるためには、Fを上げるかIPCを上げるかになるが、Fを上げると同時に消費電力も増えることになり、ある程度以上の動作周波数以上に引き上げるのが放熱の観点から困難、という制約があった。

一方IPCを引き上げるのはもっと難しい、というのはここまでの連載で紹介したとおり。いろいろな策を講じてIPCを引き上げようとしているが、それでもなかなか上がらない。例えばインテルの場合、1989年に「Intel 486DX」がリリースされた頃は、最大33MHz駆動でIPCはほぼ1命令/サイクルであった。

一方2006年に「Core 2 Duo」がリリースされた際には、Extreme Edition向けは最大2.93GHzまで動作周波数は上がったものの、IPCはやっと3命令/サイクルが実現できた程度である。17年をかけて動作周波数は約90倍になったのに、IPCはたったの3倍でしかないということからもIPCを引き上げることの難しさがわかるだろう。

そこで次なるアイデアとして出てきたのが「CPUの数を増やす」である。前回のSMT(同期マルチスレッディング)と発想は似ているが、先に登場したのは当然こちらである。複数のCPUがあれば、その性能は以下の式となる。

- P=n×F×IPC

ここでのnは「Number of CPUs」、つまりCPUの数である。33MHzのCPUであっても、3つ並べれば見かけ上は100MHzのCPU1個と同じ処理性能になるという、これまた単純なアイディアである。

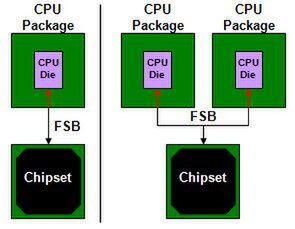

そんなわけで、x86の場合、P54C世代の「Pentium」で、初めてCPUの数を増やした構成がサポートされた。図1の左が通常のシングルCPU構成とすると、最初のデュアルCPUは図1右のようになる。FSBを共有する、という形で2つのCPUが同時に動作するようになったわけだ。

図1 Pentium世代での基本的なシングルCPU構成(左)とデュアルCPU構成

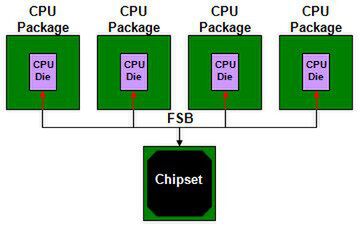

この構成、「Pentium Pro」では図2のように、最大4CPUまでを標準サポートするようになった。「標準サポート」という微妙な言い方をしたのは、4つという制限はあくまでインテルの提供するチップセットを使った場合で、サードパーティの中には6~8CPUまでの構成をサポートする製品もあった。

図2 Pentium Pro世代の4CPUのシステム構成

ちなみに、8個までのCPUをサポートするチップセットに「Profusion」という製品があった。Corollary社というチップベンダーが開発したのだが、インテルは1997年に同社を買収。その後インテルでも発売したにも関わらず(関連リンク)、今では黒歴史扱いされているという、ちょっと可哀想な運命をたどっている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ