ロードマップでわかる!当世プロセッサー事情 第808回

酸化ハフニウム(HfO2)でフィンをカバーすると性能が改善、TMD半導体の実現に近づく IEDM 2024レポート

2025年01月27日 12時00分更新

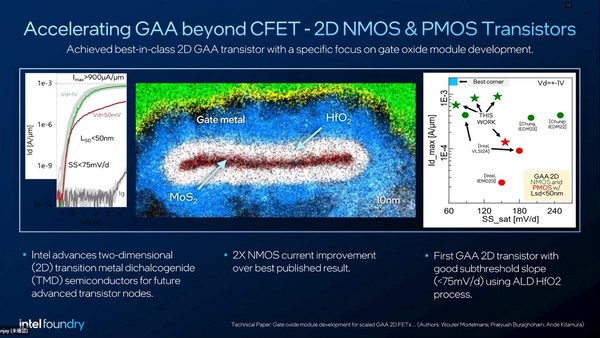

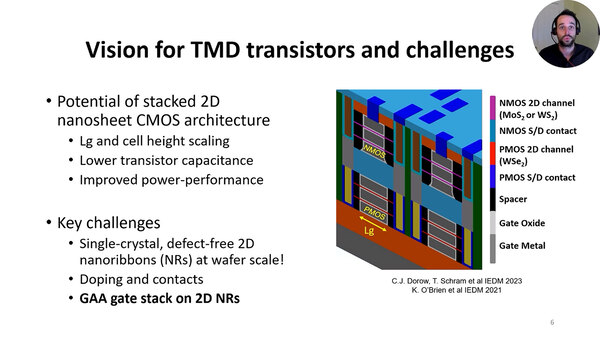

一週空いたが、IEDM 2024の第5弾は、24-3の"Gate oxide module development for scaled GAA 2D FETs enabling SS<75mV/d and record Idmax>900μA/μm at Lg<50nm"である。インテルのプレビューでは下のスライドに相当する話だ。

ゲート長30nmのGAA NMOS/PMOSを

シリコンを利用せずに構築

論文の要旨は、ナノシート型FETにおけるシリコンの代替として、TMD(2次元遷移金属二カルコゲナイド)半導体の実現可能性を向上させることを目的とした、としている。

具体的にはゲート長30nmのGAA NMOS/PMOSを、シリコンを利用せずに構築するのが目的で、インテル独自のゲート酸化膜プロセス、それと改良型のゲートクリーニングの技法により、ゲート長50nm未満で厚さ1nm未満の単層MoS2チャネルを構築し、SS<75mV/decおよびIdmax>900μA/μmという記録的な値を達成した、としている。もっともいろいろ懸念事項もあるので、単純に喜んでいるわけでもないのだが、そのあたりは後ほど説明する。

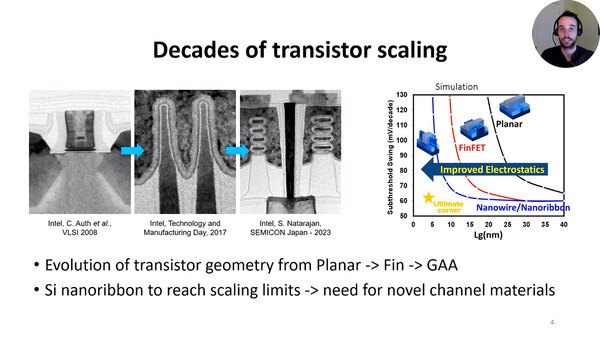

発表の内容であるが、まずこの20年弱で急速にトランジスタが進化したというのはご存じのとおり。プレナー型と呼ばれる従来のトランジスタから、3次元構造のFinFETに移行し、間もなくナノシートを利用したGAAと呼ばれるトランジスタが出現しようとしている。

FinFETを使った量産プロセスの最初の製品はインテルの22nmのIvy Bridgeなので2009年のことであり、そこから16年でGAAの量産が開始されようとしている。FinFETの時代が意外に長かったというべきか、短かったというべきか

このプレナー→FinFET→GAAでどんどんゲート長を短縮できるようになったが、それでも限界というものはある。FinFETでは30nmあたりから急速に特性が悪化する。GAAではもう少し粘れるが、それでも20nmを切ったあたりからやはり悪化するというのがシミュレーションでの結果である。

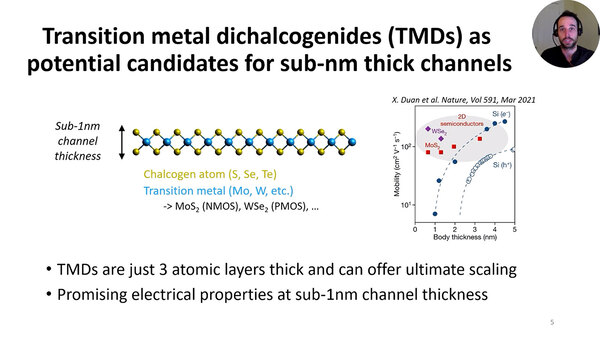

これを打ち破るための方法はいろいろ模索されているわけだが、そのうちの1つがTMDと呼ばれるものである。連載806回でも紹介したが、フィンの厚みをどんどん減らそうとすると、他の特性が悪化する。これを打ち破るための材料の1つとして期待されているのがTMDであり、さまざまな研究がなされている。

TMDそのものは原子3つ分、厚みにしても1nm未満で構成できるから、薄膜化を目指すには最適な材料である。

特にこの研究の場合、ターゲットとなるのは将来のCFET向けである。

このスライドそのものは、2024年のVLSI Symposiumにおけるインテルの発表(Record Performance in GAA 2D NMOS and PMOSusing Monolayer MoS2 and WSe2 with scaled contact and gate length)を流用している

次がCFET、という話は連載803回や連載806回でも出てきた話なので繰り返さないが、これは業界的には妥当な流れと判断されているようだ。

ただし当然ながら課題も多い。そもそもウェハーサイズ、つまり直径300mmのリボンを欠陥なく構成できるようにしないといけないというのが最初の問題だし、積層する場合のコンタクト、つまり配線層をどう作り込むかというのも問題である。またCFETに関しては、まだ実験室レベルでの積層に成功したレベルの話であって、量産で流せるような製造手法そのものが確立できていない。

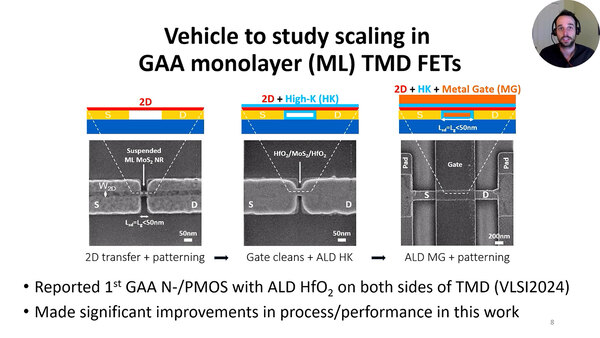

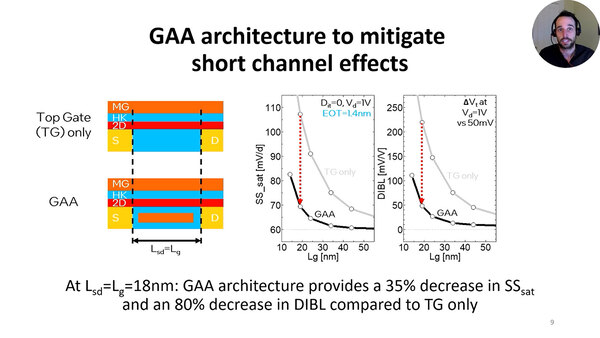

現在におけるTMDを利用したGAA FETの構築方法が下の画像である。

ALD(Atomic Layer Deposition:原子層堆積法)という技法を利用して、ゲートの周囲にHfO2の膜を積層している(水色の部分がHfO2の膜である)。このHfO2の膜を構築することで、SSsat(Subthreshold Slope saturation:しきい値以下スロープ飽和)とDIBL(Drain Induced Barrier Lowering:ドレイン誘障壁低下)という、トランジスタ特性を示す2つの値がどちらも改善されているとする。

GAAを利用することで短チャネル効果が緩和され、特性が改善したという話。短チャネル効果は連載806回で簡単に触れている

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ