ロードマップでわかる!当世プロセッサー事情 第774回

日本の半導体メーカーが開発協力に名乗りを上げた次世代Esperanto ET-SoC AIプロセッサーの昨今

2024年06月03日 12時00分更新

ET-SoC-2は予定通りなら2025年後半にサンプル出荷開始

次世代のET-SoC-3は2026年後半出荷とのことだが間に合うのか?

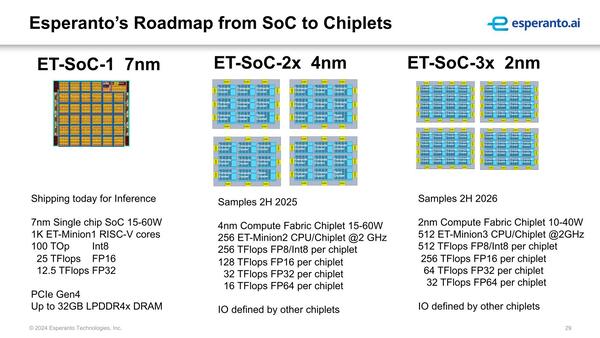

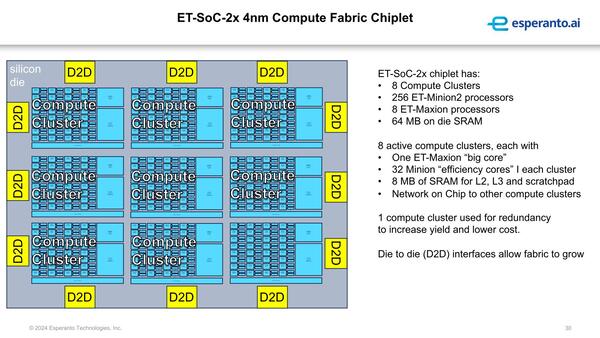

さてここからが将来製品のロードマップである。ET-SoC-1はチップ内にすべての機能を搭載しており、ここにはPCIeやメモリーコントローラーなども含まれていたが、ET-SoC-2以降はすべてチップレットになり、I/O類やメモリーコントローラーなどは外部のチップレット任せとなる。

ET-SoC-1では1088個だったET-Minionが、ET-SoC-2ではチップレット1個あたり256個になる計算で、ほぼ4分の1に減るわけだが、性能は4倍になるから「同じ動作周波数ならば」性能は同等と言う計算だ。

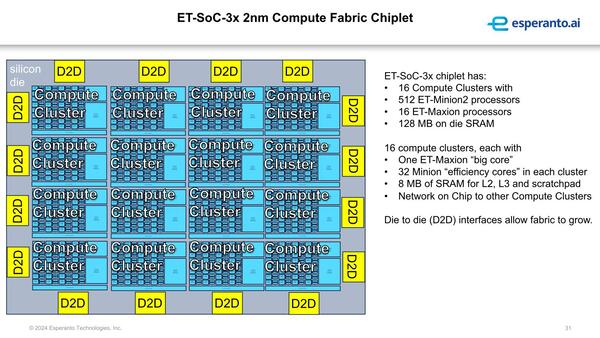

ちなみに上の画像で示すように、ET-SoC-2は9クラスター(うち有効なのが8)、ET-SoC-3は16クラスターとなる。クラスター内部に関してはET-SoC-2とET-SoC-3で基本的には同じ、という話であった。ただET-SoC-2は12個のDie-to-Die I/Fを持つ一方、ET-SoC-3は16個となる。

ET-SoC-2は12個のDie-to-Die I/Fを持つ。このD2D I/Fがどこにつながるのかがはっきりわからないが、おそらくクラスター同士をつなぐNoC(Network on Chip)に接続されるのだろう

Die-to-Die I/FはUCIeを利用しており、転送速度は32Gbpsとのこと。0.2~0.3pJ/bitで、1Tbitのリンクでも消費電力は0.5W程度との試算が出ている。

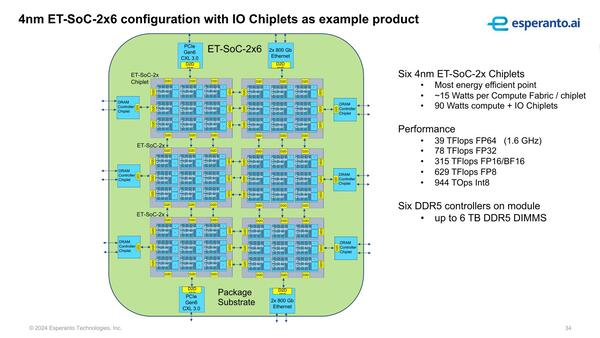

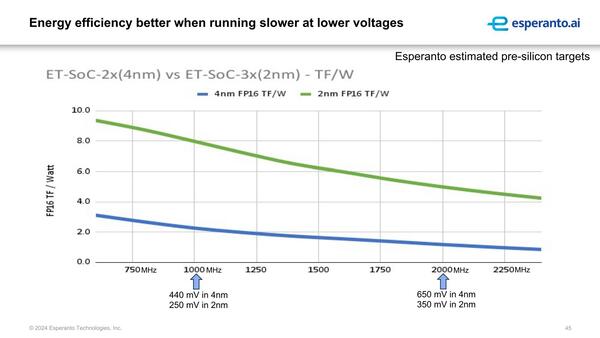

1GHz動作だと4nmが2.2TFlops/W。ET-SoC-2が1GHzで65.5TFlopsなので、消費電力はおおむね30W程になる計算だ。ET-SoC-2は133.1TFlopsだが、こちらは8TFlops/Wになるから消費電力は16W強まで落ちる

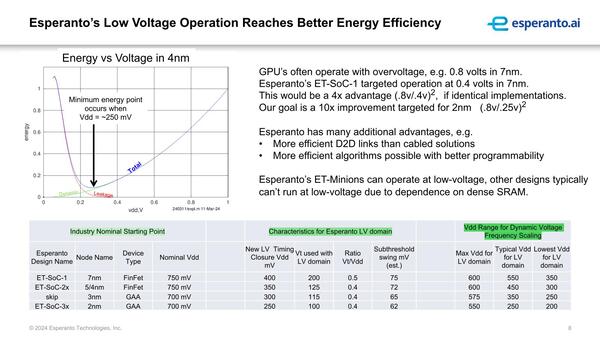

気になる動作周波数と消費電力であるが、推定で言えば1GHz動作が4nmで440mV、2nmなら250mV程度で可能になる、としている。また2GHz動作ではそれぞれ650mV/350mVということで、この2GHzの数字はわりと普通で、通常の4nmよりやや低い程度であり、ELVのメリットがまるで生かせない。おそらくは1GHz動作が標準的な数字ということになるだろう。

ただ実際の構成案を見ると、これでもまだ消費電力が多すぎる。実際には350mVあたりまで下げることを想定しているようだ。

話が前後するが、Esperantoでは第2世代のET-SoC-2を4nm、第3世代のET-SoC-3を2nmで製造することを予定している。このうち第3世代は冒頭で述べたようにRapidusで製造されるのだが、第2世代はどうもSamsungのSF4が利用されるようだ(SF4Eかもしれないが、そこまでは確認できなかった)。

まだET-SoC-2はテープアウトに至っていない(もうすぐらしい)が、2025年後半にはサンプル出荷を予定している。それはいいのだが、ET-SoC-3は2026年後半のサンプル出荷としている。Rapidusの正式なオペレーション開始は2027年度であることを考えると、さすがにこれは厳しくないだろうか? というのが正直な感想である。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ