ロードマップでわかる!当世プロセッサー事情 第774回

日本の半導体メーカーが開発協力に名乗りを上げた次世代Esperanto ET-SoC AIプロセッサーの昨今

2024年06月03日 12時00分更新

Esperantoが日本の半導体メーカーRapidusと協力

5月15日、都内でRapidus(ラピダス)とEsperanto Technologyが共同で記者会見を開催、Esperanto Technologyの第3世代製品をRapidusの2nmプロセスを利用して製造することに関してのMOU(協力覚書)を交わしたことを明らかにした。

左がRapidusの小池淳義社長、中央がEsperanto TechnologyのArt Swift氏(CEO&President)。右は通訳を務めた笠原栄二氏(Senior Architect, Esperanto Technology)

といってもまだMOUのレベルであって、具体的に契約が交わされたわけではない。そもそも現状ではまだRapidusの方が工場すらなく、サンプル品を作るどころかテストベッドすら走らせられない。

また製造装置すら確定していない状態ではPDK(Process Development Kit:チップの物理設計を行なう際に必要となるさまざまなパラメーターをまとめたもの)すら出せないから、Esperanto側としても物理設計を始めることすらできない。

この状態でさすがに契約というのは双方にとってハイリスクな行為であり、その前段階である協力覚書に留まるのは当然である。

それは良いとして、記者会見では2nmが主な話題であって深い話はなかったのだが、Esperanto Technologyは今年4月に東京大学で開催されたCool Chipsで第2および第3世代のET-SoCに関して同社創業者にしてCTOのDavid Ditzel氏が講演しており、ここで多少の説明をしている。今回の記者説明会にはもDitzel氏が同行しており、少し細かな話をうかがえたので、これをもとにET-SoC-2/ET-SoC-3の詳細を説明したい。

発端はRISC-VベースのAI向けプロセッサー「ET-SoC-1」

電圧を大幅に下げて性能/消費電力比を大きく向上させた野心作

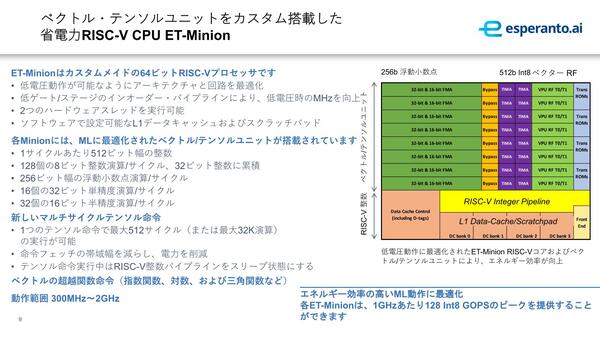

まずおさらいを。連載645回で説明したが、同社のET-SoC-1は、ET-Minionというコアが基本となる。ET-MinionはIn-OrderのRISC-Vコアに、512bit幅のVector/Tensor Unitをアクセラレーターの形で組み合わせたものだ。

このVector/Tensor Unitが肝であり、FP16なら32個、FP32なら16個の演算を1サイクルに実行可能である。またTensor Unitとして使う場合、最大512サイクル連続して稼働できる。

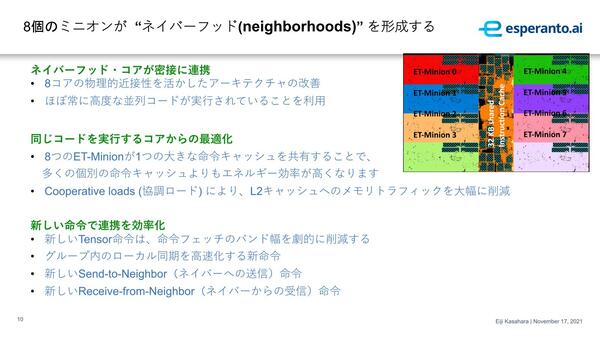

そして8つのET-MinionをまとめてNeighborhoodsを構成し、この8つのET-MinionでL1命令キャッシュを共有する。このNeighborがある意味、1つの処理単位と考えればいい。

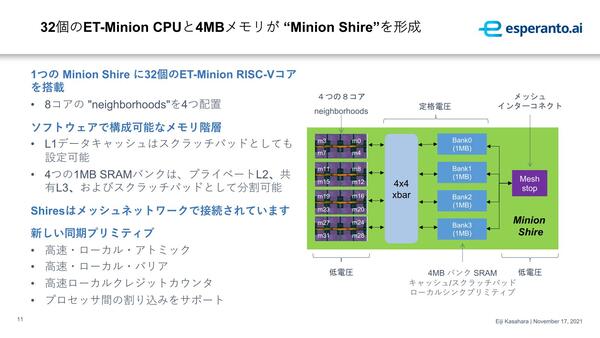

L1を共有というのは、8つのET-Minionコアが同じ命令を実行するから(データは異なる)である。Neighberhoodsを4つと、1MB×4のSRAMを組み合わせたものがMinion Shireとなり、CPU内のほかのMinion Shareとのメッシュ接続のI/Fもここに搭載される格好になる。このMinion Shareが事実上の最小構成というわけだ。

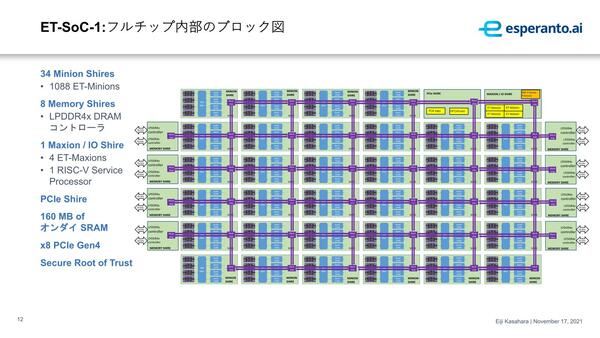

ET-SoC-1全体は、このMinion Shareを34個、それとアプリケーション/OS用のET-Maxion×4、さらにPCIeのブロックと8つのLPDDR4x I/F(各々32bit幅)から構成される格好になる。合計で1088個のET-Minionが搭載され、そのおのおのに512bit幅のVector/Tensor Unitが搭載される形になる。

厳密に言えば、他にもう一個RISC-V Service Processorがシステム全体の管理用に動作するが、これはアプリケーション側からは見えないようだ。

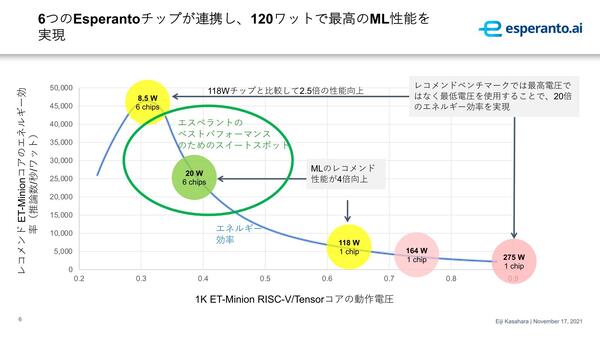

さて、ここまで言えば単にMassive Parallelの一種と見えなくもないET-SoC-1であるが、最大の特徴は電圧を大幅に下げて性能/消費電力比を大きく向上させていることだ。

今回はこの技術をELV(Extreme Low Voltage)と呼ぶようになったのだが、要するに通常よりも大幅に電圧を下げることで効率向上を図る、というものだ。ET-SoC-1の場合はおおむね以下の試算が成立する。

| ET-SoC-1のスペック | ||||||

|---|---|---|---|---|---|---|

| 電圧 | 性能消費電力比 | 消費電力 | 性能 | |||

| 0.31V動作 | 4万7000OPS/W | 8.5W | 240万OPS/6chip | |||

| 0.38V動作 | 2万5000OPS/W | 20W | 300万OPS/6chip | |||

| 0.63V動作 | 6000OPS/W | 118W | 70万8000OPS/1chip | |||

| 0.74V動作 | 4000OPS/W | 168W | 67万2000OPS/1chip | |||

| 0.9V動作 | 2500OPS/W | 275W | 68万7500OPS/1chip | |||

PCIeカード1枚の消費電力枠を120Wとすると、0.63V以上では1チップでカードの消費電力枠を使い切ってしまう。0.38Vでは6チップが搭載できて、トータルの性能が一番高い。ちなみに0.31V枠なら14個チップを搭載可能で、この場合は560万OPSが発揮できるはずだが、14個も1枚のカードに載せられないという物理的な障害があるため、そのあたりを勘案すると0.38V動作がちょうどいい、という判断らしい。

もちろん通常の7nm(TSMC N7)では、こんな低電圧での動作は不可能である。そのあたりがDitzel氏というかEsperantoのノウハウが一番生きる部分というわけだ。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ