GPUでいうところの4TOPS相当の性能

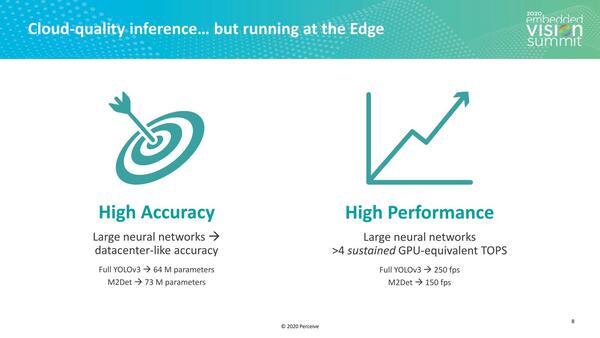

Perceiveの最初のチップであるERGOは、エッジというよりもエンドポイントに利用できるサイズと消費電力でありながら、高い性能と精度を目指したとするが、この精度と性能に関しては明確な指針が出ている。

まず精度については、現状データの持ち方(INT1/2/4/8/FP8/BF16/....)よりもネットワークの規模や、そこで利用されるパラメーター数の方が支配的である。

したがって、フルセットのネットワークが稼働する(≒そのネットワークで利用されるパラメーターをオンチップで保持できる)ことが目標となる。また性能に関しては「GPUでいうところの4TOPS相当」という数字が示された。具体的にはYOLOv3で250fps、M2Detで150fpsとされる。

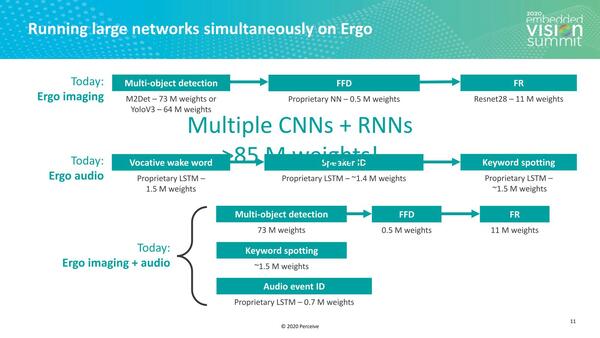

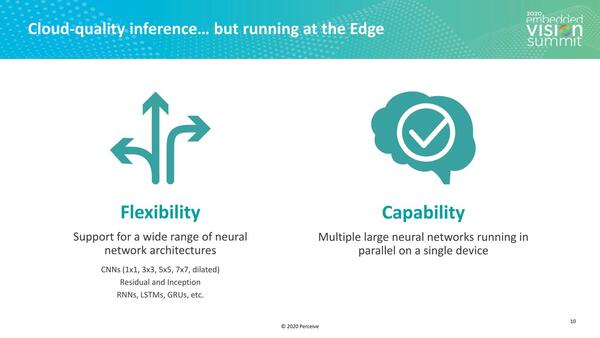

加えて、さまざまなネットワークに対応できる柔軟性と、複数のネットワークを同時に稼働できる容量が必要、という欲張りぶりである。

これは例えばAspinityのように、特定のネットワークに絞った実装では不十分、ということである

この複数のネットワークに関しては実際に、イメージングだけ、オーディオだけ、イメージングとオーディオという3種類の実装例が示された。

こうした複数のネットワークを同時に動かすとなると、処理性能だけでなくパラメーターを搭載するためのメモリーもそれなりに必要になってくる(さもないとパラメーターのロードがボトルネックになる)。

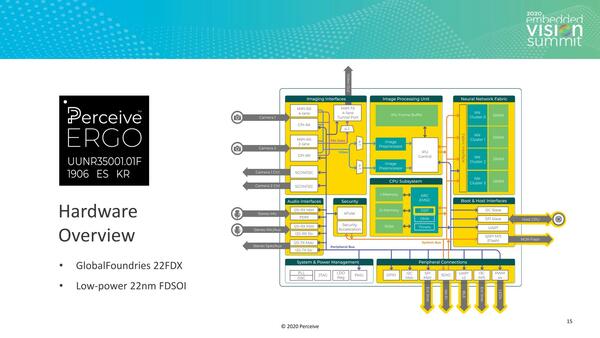

さて、ここまで説明してきておいてなんだが、Perceiveはこれを実現したERGOチップの詳細をまったく明らかにしていない。ERGOチップの内部構造が下の画像で、イメージングI/FとオーディオI/F、IPUとCPUサブシステム、それにNNファブリックがあるが、そのNNファブリックがどんな構成でどのくらいのSRAMが搭載されているか、などは一切未公開なままである。

CPUサブシステムはSynopsysのArm EM5Dがベースで、DSPが拡張されている程度。基本的にはシステム制御で、ここでNNを動かしたり音声/画像処理を行なったりはしないと思われる

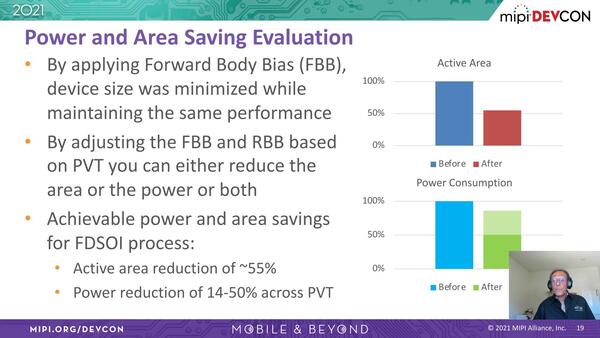

ただ省電力を実現できた理由の1つとして、Globalfoundriesの22FDXプロセスを利用し、さらにFBB(Forward Body Bias)とRBB(Reverse Body Bias)の両方を利用したとしている。

なぜかこの説明はMIPI DevCon 2021で、説明もMIPI I/FをPerceiveに提供したMixelのCEOであるAshraf Takla氏が行なっているが、察するに単にIPを提供しただけでなく、物理設計でも協力していたように思われる

説明によれば、高速動作が必要な部分にFBBを利用することで、アクティブ部分のエリアサイズを最大55%削減、その一方でその他の部分にはRBBを利用してトータルで14~50%の省電力化を図った、としている。

ちなみにチップの外形寸法は7×7mmとされるが、全体の3分の2以上はNNクラスターとSRAMが占めるという説明があった。Globalfoundriesが2017年のVLSI Symposiumで発表した数字によれば、22FDXを利用した場合のSRAM Cellの面積はHD(High Density:高密度)で0.110μm2、HC(High Current:高速)で0.124μm2とされる。

今回の場合はHDを利用しているだろうから、0.110μm2ということになる。パッケージが7×7mmだからといってダイサイズは当然もっと小さいはずだが、具体的な数字は示されていない。

ただ仮に5×5mmとして、そのうち3分の2がNNクラスター+SRAMで、そのSRAMの面積が4分の3くらいだと仮定すると、SRAMのサイズは12~13mm2程度。ざっと計算しても全部で13.5MB程度の容量が精一杯に思われるのだが、これで合計85M以上のパラメーターをどう保持しているのか、はけっこう謎である。

もちろんパラメーターは疎の部分があるので、うまくSparsityを管理して、さらにパラメーター圧縮などを行なっているのかもしれないが。

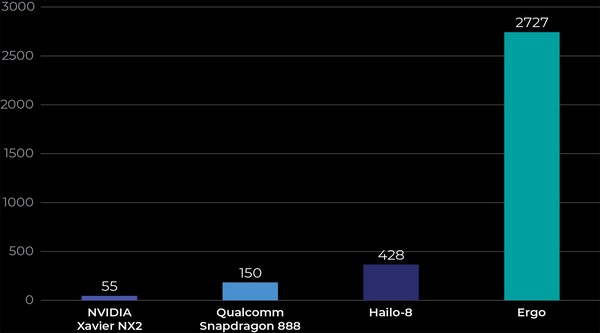

このERGOチップはすでに出荷を開始しており、評価ボードも出荷されている。製品の方は定格(250MHz動作)とLow Power(250MHz動作ながらVDDを0.65Vに下げたもの)、High Performance(310MHz動作)の3つが用意されており、性能/消費電力比は圧倒的に高いとしている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ