NVIDIAのV100に比肩する性能

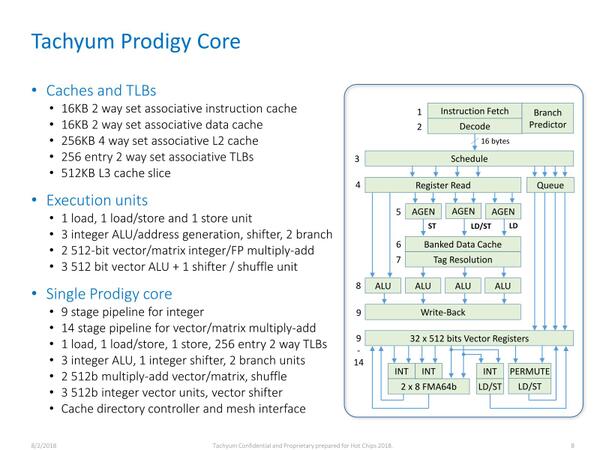

Prodigyのパイプライン構造が下の画像である。もちろん分岐予測は必要(でないと動的な判断を入れた瞬間にパイプラインが全フラッシュされる可能性がある)ではあるが、いわゆるフロントエンドはおそろしく簡素である。Schedulerが入るのは、通常のALU以外にベクトルALUが入るためであろう。

AI向け処理に関しては、むしろメインと分離されたベクトルユニットの方が活用されると思われる。後述するが、FP8をすでにサポートしており、なかなか先見の明がある気がする。INT4が未サポートなのは残念である。とはいえ、2018年の時点でここまで見通すのは難しいだろう

In-Orderで9段というのは結構長めであるが、そもそもVLIWの時点で1段あたりの処理量はかなり少ない。それでも9段にした理由は以下の2つが考えられる。

- 1段あたりの処理を最小にすることで、動作周波数の引き上げを狙った

- キャッシュからのロードに時間がかかることを考慮して、ALUを動かすまでのサイクル数を長めに取った

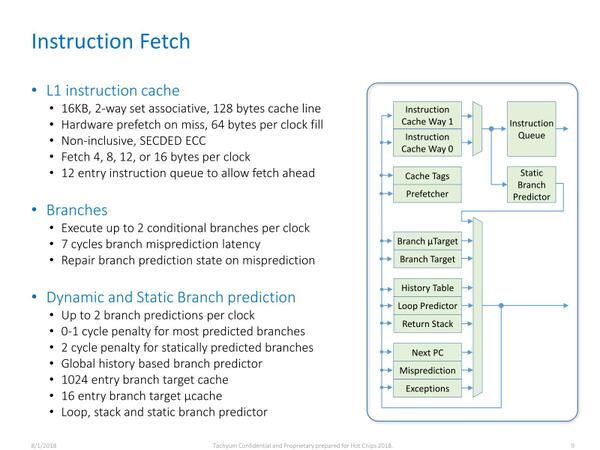

Tachyumはもう少しProdigyの詳細を公開してくれている。まず命令フェッチ段は下の画像の通り。

分岐予測はVLIWとしてはかなり充実している気はするが、昨今のOut-of-Orderを実装したCPU(それこそAlder LakeやZen 3など)に比べればかなりシンプルではある。むしろペナルティーの少なさが特徴的で、分岐ミスのペナルティーが7サイクルというのはIn-Orderならではだろう。といっても、9サイクルのパイプラインで7サイクルなので、ほぼパイプライン・フラッシュに近いという言い方もできる。

ALU側のパイプラインは下の画像の通り。投機的なデータロード/ストアは、実際にそれが必要になるまでホールドされるのは、In-Order型のパイプラインとしては当然ではある。

プロセッサーの構造を複雑にして、エリアサイズ増大など複雑なメカニズムを搭載するのではなく、素直にIn-Order型の処理で済ませるような実装になっているのは、むしろ自然だとは思う。もともとIPCを無理に引き上げるよりも、多数のコアを同時に走らせることで効率よく処理する構成なので、このあたりはトレードオフとして妥当な実装に見える。

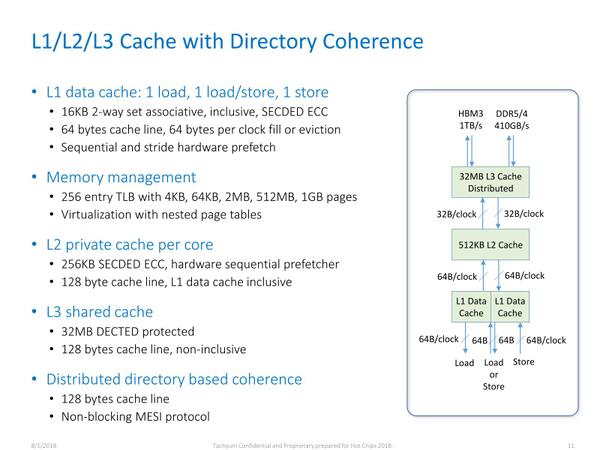

キャッシュは、L1(16KB)+L2(512KB)がコアごとにあり、L3が共有32MBとなっている。L3がExclusive Cache(排他的キャッシュ)なのは、Prodigyの使い方ではコア間にまたがって共有するようなデータがあまり多くないことを考えれば妥当に思える。

64コアで32MBなのでコアあたり512KBという計算で、これをInclusive Cache(包括的キャッシュ)にしたら全然意味がなくなってしまう。その意味でもL3が排他的になっているのは必然だったともいえる。

演算性能のメインとなるのがベクトルユニットである。512bit幅のユニットで、MACなら2演算/サイクル、単純な算術演算なら3演算/サイクルが可能、というのはこの手のものとしてはかなり高性能(AVX512並)である。

FP64でMAC演算すると、1サイクルあたり8×2×2=16Flopsとなる。4GHz駆動ならばコアあたり128GFlops、これが64コアなので8TFlopsという計算になる。

オークリッジ国立研究所に納入されたFrontierで動くAMD Instinct MI250Xが1枚あたり45TFlops、つまりダイ1つあたり22.5TFlopsなことを考えればやや見劣りするという言い方もできるが、2018年時点で言えばNVIDIAのVoltaベースのV100がやはりFP64で7.8TFlopsだったことを考えれば、V100に比肩する性能を叩き出す計算になる。

これを支えるインターコネクトの構成が下の画像だ。メモリーコントローラーは全部で8chあり、そこからメッシュの形ですべてのコアに対して1clock/hopでアクセスが可能になっている。

性能と消費電力、コストを考えるとHBM3を載せるのは非現実的だとは思う。DDR5では1本のDIMMで2ch動作することはこの構造に盛り込まれていないようだ。2018年の時点でそこまで予見するのは不可能だっただろう

ここで見るとHBM3に関してはあまり考えていないというか、DDR4/5のキャッシュみたいな使い方になっている。実際DRAM cacheないしMemory Regionの2つというあたりは、少なくともアプリケーションからこれを細かく制御する使い方は考えていないようだ。

可能性としては、広帯域が必要となるアプリケーションと、通常帯域で足りるアプリケーションを分けて、別のメモリーアドレスに割り振るといった使い方も可能だとは思うが、どこまで現実的かを考えると難しい気もする。

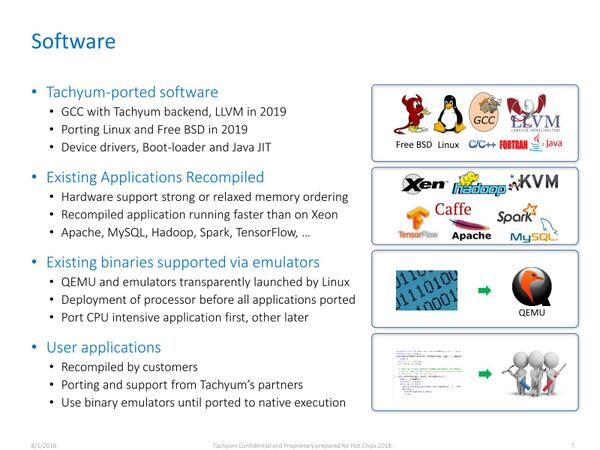

最後が肝となるソフトウェアである。一応GCCやLLVM、Linux/FreeBSD、ドライバーなどはすべてTachyumが移植を行ない、一方QEMUなどに関してはエミュレーション動作でカバーすることになっている。とはいえこの時点ではまだコンパイラの出来などを議論するには時期尚早といった感じではある。

この連載の記事

-

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 - この連載の一覧へ