ロードマップでわかる!当世プロセッサー事情 第673回

インテルがAIプロセッサーに関する論文でIntel 4の開発が順調であることを強調 AIプロセッサーの昨今

2022年06月27日 12時00分更新

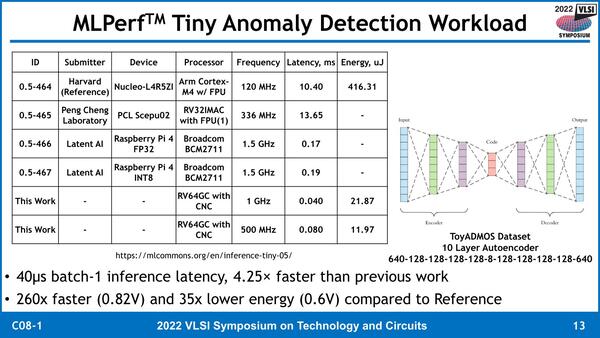

汎用品と比べて性能は260倍、エネルギー効率は35倍

おそろしく効率の良い演算が可能

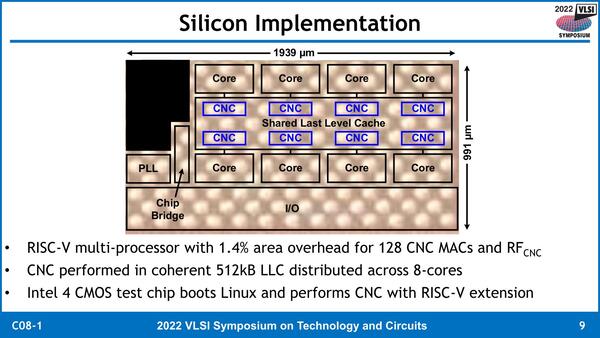

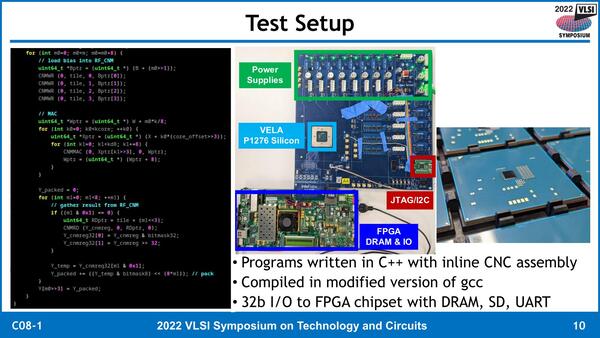

今回インテルはIntel 4プロセスを使ってこのプロセッサーを製造している。CNCを追加したことによるオーバーヘッドはエリアサイズの1.4%増加程度に留められている。プログラムはほとんどの部分がRISC-V用のコンパイラを使ってC++で記述され、今回追加したCNC向けはインラインアセンブラで記述、というやり方で試したそうだ。

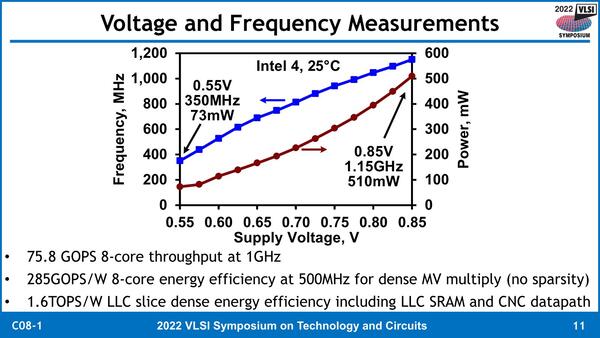

下の画像は電圧と動作周波数および消費電力をまとめたものである。青い方は電圧-動作周波数の関係で、0.55Vで350MHz、0.75Vで1.15GHz動作となっている。

CVA6のような単純な(つまりパイプライン1段あたりの処理が大きく、動作周波数を上げやすい)コアでも0.85Vで1.15GHz動作するという話であり、その際の消費電力は0.55Vでわずか73mW、0.85Vでも510mWでしかない。

一方で性能の方は、8コアを1GHzで動かしたときに75.8GOPSほど。1GHzでは消費電力は400mW程度なので、性能は189.5GOPS/Wほどになる。500MHzまで落とすと285GOPS/W、LLCだけの消費電力で言えば1.6TOPS/Wという、おそろしく効率の良い演算が可能になる、とされた。

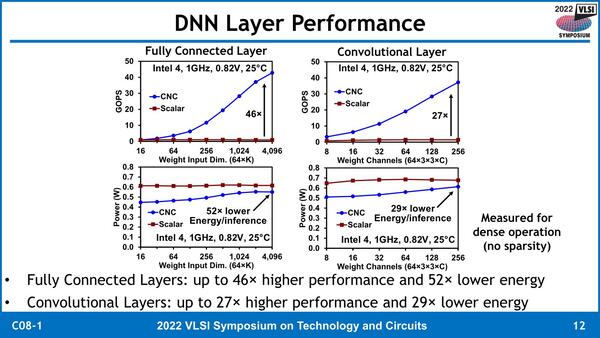

さて上で説明したように、CNCは汎用というよりはもう明確に畳み込み演算に特化した構造になっているわけで、当然ながらAIというか畳み込みニューラルネットワークでの処理性能が重要になってくる。これに関して、CVA6の内蔵エンジン(スカラー:赤)と、CNC(青)を利用した場合の性能を、全結合層と畳み込み層で比較したのが下の画像である。

スカラーを使うと、とにかく性能が低いというか全然話にならないし、ウェイトデータの次元数やウェイトのチャネルが増えても全然性能が上がらないが、CNCではどんどん性能が改善し、しかも消費電力そのものはスカラーより低めだから、エネルギー効率は52倍や29倍という話になる。

もう少し現実的な比較としては、MLPerfのTiny Anomaly Detectionを実施してみた結果がこちら。This Workというのが今回のもので、他のNucleoやRaspberry Piなどは、すでにMLPerfに登録されている結果である。

2つ目のPeng Cheng Laboratoryは32bit RISC-Vコアを使ったものだが、ボードの詳細が不明である。ひょっとしてFPGAかなにかで実装してテストした結果なのかもしれない(消費電力が示されていないあたりがいかにもそれらしい)

ただこれも、汎用のRaspberry Pi 4を使ったとか、一番上のNucleo-L4R5ZIに至ってはSTMicroelectronicsの出している開発ボードであるSTM32 Nucleo-144を使ったものなので、性能比較の対象としてどうだろう? という気はするのだが、とりあえずこうした汎用品と比べてレイテンシーは4分の1未満であり、性能は260倍、エネルギー効率は35倍にもなる、という説明であった。

インテルがこれを直近の製品に投入する可能性は少ない。Meteor LakeはMyriad Xないしその次期製品を統合するらしいという話は連載657回で説明したが、実際に統合されるのは第3世代のVPU(つまりMyriad Xの次の世代のもの)になるとのことだ。

ついでに言えばこの第3世代のVPUは単体カードでの提供の予定はなくなり、Movidiusのチームは全部CCG(Client Computing Group)に移籍したとかで、今後はCoreプロセッサーの中のアクセラレーターとして提供されることになる。したがって、直近はこのMovidius由来のものが使われることになるだろう。ただ長期的には、PIMというかCNCというか、そうしたモデルがAI向けにはけっこう有用ということが今回の論文で示された格好だ。

ちなみにこの論文の影の役割は、「Intel 4が確実に来そう、と人々に信じさせること」である。今回RISC-VコアをIntel 4で製造して見せたというのは、IFS(Intel Foundry Service)がRISC-V Internationalに加盟してRISC-Vコアの製造をサポートし、またIFSの最初の汎用ロジック向けがIntel 3であることを考えると、「この通り作れます」というアピールになるわけだ。

冒頭でIntelがVLSI Symposiumで論文を12本を出した、という話をしたが、このうち以下の5本がIntel 4に絡めたものになっている。

| VLSI Symposium 2022で発表されたIntel 4に関する論文 | ||||||

|---|---|---|---|---|---|---|

| T01-1 | Intel 4 CMOS Technology Featuring Advanced FinFET Transistors optimized for High Density and High Performance Computing | |||||

| C08-1 | An 8-core RISC-V Processor with Compute near Last Level Cache in Intel 4 CMOS | |||||

| C13-3 | A 90.9kS/s, 0.7nJ/conversion Hybrid Temperature Sensor in 4nm-class CMOS | |||||

| C16-1 | A 7Gbps SCA-Resistant Multiplicative-Masked AES Engine in Intel 4 CMOS | |||||

| C24-1 | Energy-Efficient High Bandwidth 6T SRAM Design on Intel 4 CMOS Technology | |||||

冒頭のT01-1はそのものズバリIntel 4の詳細だが、それ以外にIntel 4を利用した回路の論文を4つも出すあたり、インテルとしてはこんな形でIntel 4が順調であることを強調する必要性がある、というあたりが逆にIntel 4に不安を感じさせる。筆者の勘繰り過ぎだと良いのだが。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ