重要な役割を果たすバイパスコンデンサー

ここで基本的な回路の話をしておこう。パスコン、いわゆるバイパスコンデンサーというものはものすごく広く利用されており、特に昨今のCPUやGPUなど大電流を要求するチップでは欠かせないコンポーネントである。このバイパスコンデンサー、役目としては2つある。

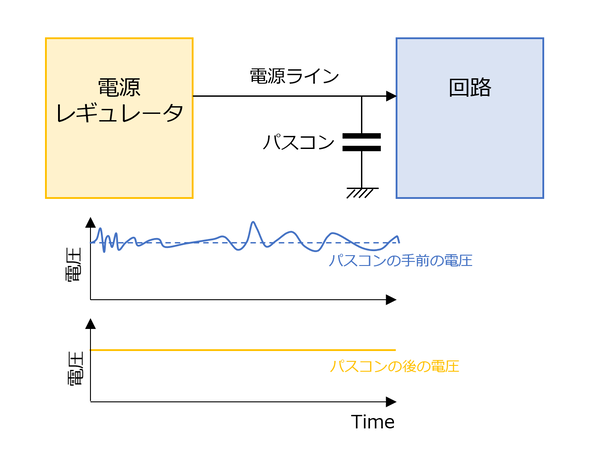

1つは供給電源ラインに混在した高周波ノイズの除去。回路は当然直流電流が来ることを想定して組まれているが、ここに高周波ノイズが混入することがあり得る。そこで回路の手前にコンデンサーを入れてやることで、高周波分をGND側に流し、回路に安定した電圧を供給するというものだ。

この際、パスコンと回路の間で改めてノイズが混入することを防ぐために、パスコンはなるべく回路に近いところに入れるのが原則である。

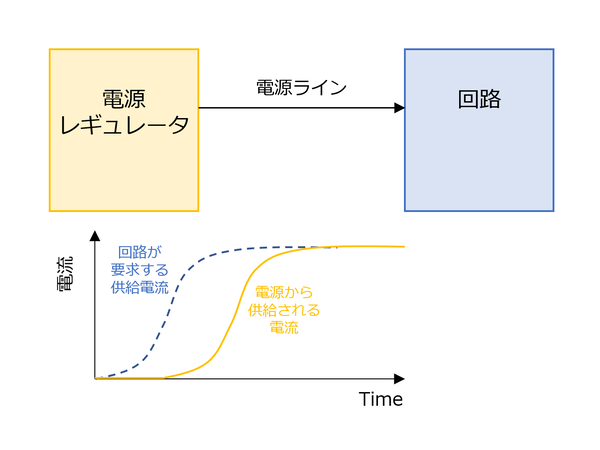

もう1つが不足する電流供給を補うというものだ。例えば回路がフルに動き始めると、必要になる電流が増えることになる。この場合、電源回路に対して供給電圧を増やすように要求し、これを受けて電源側が供給電力を増やすことになるのだが、どうしてもリクエストをだしてから実際に電流が増えるまでの間にタイムラグが生じる。

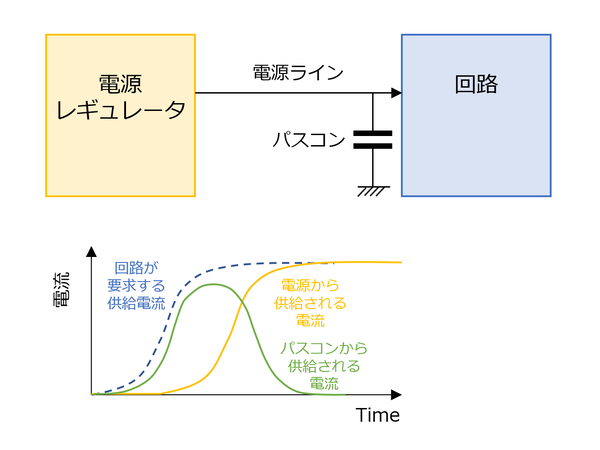

このタイムラグの間、つまり実際に供給電流が増えるまでの間は、回路はフルに動かせない。ところが電源と回路の間にパスコンを挟んだ場合、仮に電流が足りない間はパスコンから不足分の電流を一時的に供給できる。この結果、電源からの分とパスコンからの分の合計で、回路にはかなり要求に近い電流が供給されることになり、回路はそれほど待ちがないままにフル稼働できるようになる、というものだ。

ちなみにコンデンサーなので、一度放電すると次は蓄電のモードに入るわけだが、放電しきったころにはすでに電源回路から十分な電流が供給されているので、これを利用して次の放電に備えた蓄電ができるわけである。

ちなみに上図では電流の変化として説明したが、通常電流が増えるのは電圧を増やした場合である。つまり、回路が必要とする電圧と、実際に供給される電圧が一致していない間はパスコンから回路に電流が流れ、電源回路の側が電圧を上げていくにつれパスコンからの供給は減っていき、パスコン自身の蓄えた電圧より電源からの電圧が高くなったらパスコンは蓄電に切り替わるという仕組みになっている。

こういう性質のものだから、CPUのように高速な回路にパスコンは欠かせない。連載398回でRyzenのMIMCapを説明したが、なるべく回路に近いところになるべく大きなパスコンを配せば、それだけ高速動作がやりやすくなることになる。

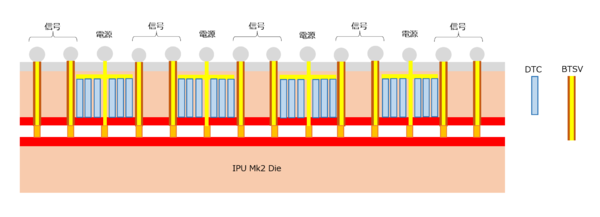

ということで話をBOWに戻す。前のページのBOW模式図をもう少しわかりやすくしたのが下図である。

IPU Mk2 Dieから出て来た信号ピンは、そのままBTSV経由でC4 Bumpに接続される。一方で電源ピンに関しては、もちろんTSV経由でC4 Bumpにつながるのだが、その途中にウェハー内に構築されたDTCベースのパスコンと接続されている構成だ。

これにより、回路の非常にそばに、ほぼIPU Mk2と同じ容積を持つパスコンが接続されているということになる。もともとIPU Mk2は823mm2と巨大なダイであり、周囲にパスコンを配しているとは言え、ダイ中央付近の電源ピンに関してはどうしてもパスコンからの距離が長くなるから、効率は悪い(それもあってパッケージ中央にBallを置かず、ここにパスコンを配する例もいくつか存在する)。

ところがBOWの方式だとすべての電源ピンに対して結構な大容量のパスコンを配することができるので、動作周波数をより引き上げても電力不足に陥ることがなくなる、というわけだ。

この方式のメリットは、追加するウェハーの方は先端プロセスである必要がまったくないことだ。つまりBTSVとDTCを構築するだけなので、28nmである必要すらなく、40nmや55nmあたりでも十分お釣りがくる(ひょっとすると90nmあたりかもしれない)。

ウェハーの製造コストは40nmだと7nmの1/4、65nmだと1/5、90nmだと1/6程度に収まっている。もちろんSoIC WoWで重ね合わせをするのに追加のコストは必要になるが、そもそも配線ピッチがC4 Ballと同じなので、AMDの3D V-Cacheに比べると精度的にはるかに緩いわけで、追加コストはそう多くない。

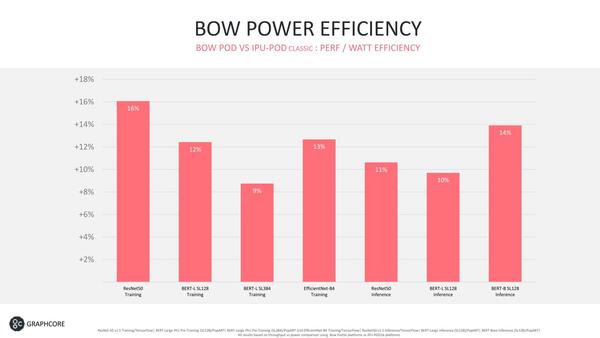

今回Graphcoreが、BOWは追加コストなしで提供すると発表したのも、この方式なら非常に安価に実装できるからということの裏返しと考えていい。ついでに言えば、これによりIPU Mk2と比較して10%前後の性能/消費電力改善が実現したというのもメリットの1つである。

ちなみにパッケージとしては上図が上下逆になった形で実装されるので、ヒートシンクの真裏に回路層が来るわけで、ここは以前と同じである。また基板に逃げる熱についても、BTSV経由で放熱できるので、特に悪化はしていないと考えられる。この技法、Graphcore以外にも採用されそうな感じだ(特許をGraphcoreとTSMCのどちらが持っているか次第だが)。

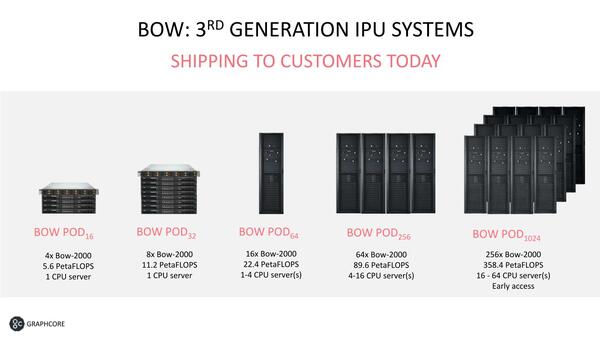

このBOWは、従来と同じように4チップを収めた1Uのブレードサーバーの形で提供されるが、最小構成のBOW POD 16(16チップ)~BOW POD 1024(1024チップ/16ラック)までが用意され、同日から出荷開始とされている。

前回の記事の最後で、5nm世代に移行するだろうと予測したが、いろいろな意味で予測が裏切られた格好だ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 - この連載の一覧へ