連載622回でGraphcoreのIPUを紹介した。そのGraphcoreが、今年3月3日に第3世代のIPUであるBOWを発表した。

このBOW、TSMCのSoIC-WoWを使って製造されたチップとなっている。ただSoICの使い方があまりに斬新すぎるので、今回はこのBOWを紹介したい。

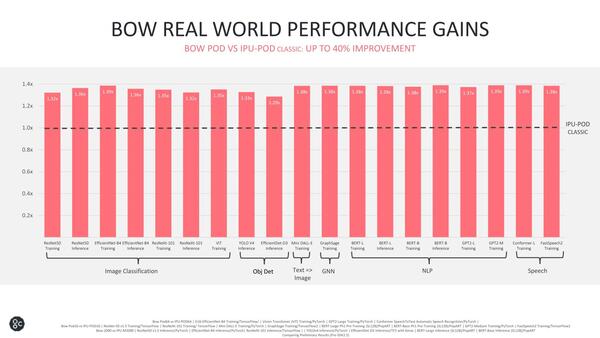

IPU Mk2から40%性能が向上し

価格はIPU Mk2と同じという「BOW」

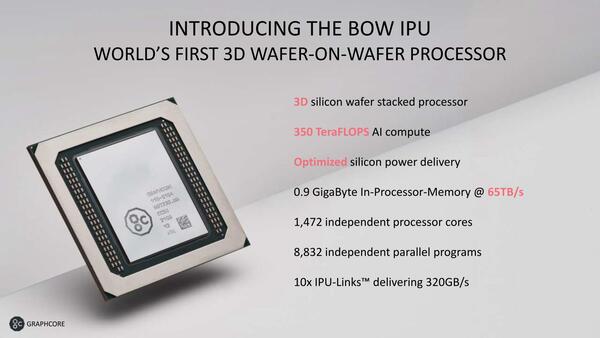

そもそもBOWの名前の由来について一切説明がない(まさかRed君の鳴き声というわけでもないと思うのだが……)のだが、そのBOW IPUの概略が下の画像だ。

BOW IPUの概略。パッケージそのものは基本変わらず。以前の第2世代IPUのシリアルが“115-0084 T6N390.00”、BOWが“115-0804 N9T238.00”というあたりでしか見分けがつかない

IPU Mk2とスペックを比較してみると、とりあえず“3D Silicon wafer stacked processor”を置いておくとして、以下のようになっており、ハードウェア的には基本一緒である。

| IPU Mk2とBOW IPUの比較 | ||||||

|---|---|---|---|---|---|---|

| 性能 | 250TFlops→350TFlops | |||||

| メモリー容量 | 900MB→0.9GB(要するに変わらず) | |||||

| メモリー帯域 | 47.5TB/秒→65TB/秒 | |||||

| IPU Core数 | 1472→1472(変わらず) | |||||

| プログラム実行数 | 8832→8832(変わらず) | |||||

| IPU Links | 10x 320GB/秒→10x 320GB/秒(変わらず) | |||||

では性能やメモリー帯域の違いは? という話だが、動作周波数が1.35GHz→1.85GHzと37%ほど向上しており、これが性能向上(40%)やメモリー帯域向上(36.8%)につながった。

この結果として、主要なアプリケーションについて、軒並み30%台の向上が得られたというのが同社の説明である。

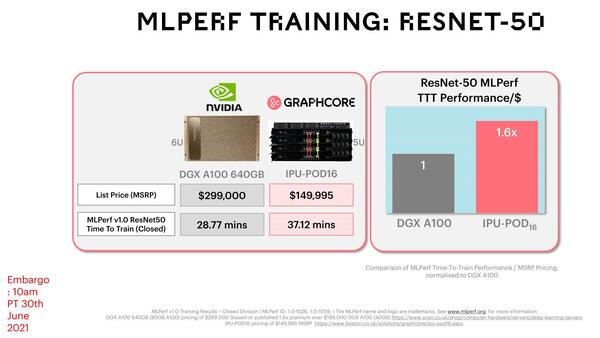

IPU Mk2(グラフではIPU-POD Classicと表現されている)とNVIDIA DGX A100の比較結果は連載622回で紹介した通りで、例えばRESNET-50の学習時間を比較するとDGX A100が28.77分、対してIPU-POD16では37.12分だったのが、これが1.32倍高速になって28.12分程度にまで高速化される計算になり、DGX A100と同程度のピーク性能でありながら、価格は半額のまま据え置きで、性能/価格比は2倍まで向上、というのが同社の説明である。ちなみにBOW IPUは価格がIPU Mk2とまったく一緒である、とされている。

ところでどうやって性能を向上させているか? であるが、構造を変えずにIPUを作り替えた(例えばTSMC N6に移行した)という話か? と思ったら、“BOWのダイは、IPU Mk2とまったく一緒(exact same)だ”という説明があった。

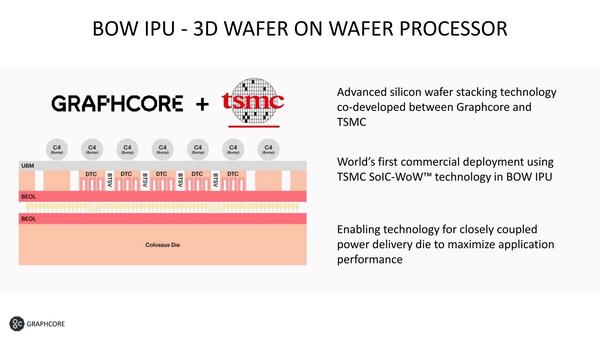

それでは3D Stackingはどこに出てくるのだ? となるわけである。通常3D Stackingと言えば、ロジックプロセスないしSRAMを積層するという話が思いつく。ただIPUの数は同じなのでロジックの積層はあり得ないし、SRAMを積層すればメモリーが増えるわけで、これもない。これに関しての同社の説明が下の画像だ。

この図では上下がひっくり返しになっているが、要するにIPU Mk2のダイをそのままに、従来だったらC4 Bumpの形でBallが出ていたところを一度取り去り、そこにウェハーを挟んで、その上にC4 Bumpを改めて構成した格好だ。

間に挟まっているウェハーであるが、その中身はBTSV(Back-side Thought Silicon VIA)とDTC(Deep Trench Capacitor)である。BTSVは、IPU Mk2から出た信号をC4 Bumpまで伝えるのが仕事である。DTCは、シリコンに溝を掘りそこをコンデンサーとして使う技法で、eDRAM(Embedded DRAM)などでも利用されているものである。現在のDRAMはDTCで構成されているので、その意味ではDRAMそのものと誤解しそうである。

これを見て「トップウェハーにeDRAMを積層したという理解でいいのか?」といった質問が殺到したが、答えはNo。なんと同社はこのDTCを、パスコン(バイパスコンデンサー)として使うという、前代未聞の実装を披露してくれた。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 - この連載の一覧へ