ロードマップでわかる!当世プロセッサー事情 第645回

ET-SoC-1の設計思想で納得、やっぱりEsperantoはDitzel氏の会社だった AIプロセッサーの昨今

2021年12月13日 12時00分更新

100~1000TOPSのピークレートを

1つのET-SoC-1で実現できる

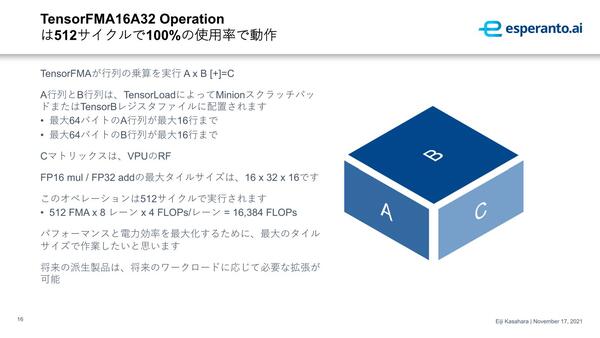

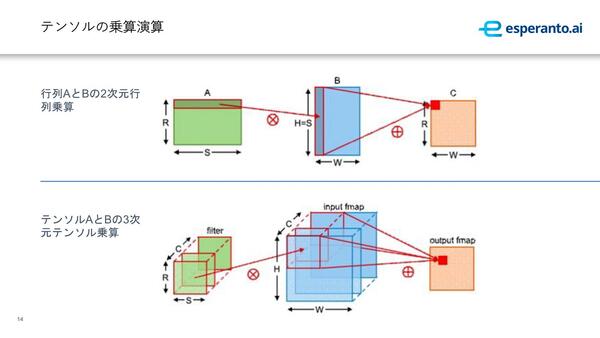

ちなみにテンソル命令でどんなことができるのか? というのが下の画像だ。

テンソル命令でできること。こうなってくると、ET-Minionの効率は「どれだけ扱うデータがこのテンソル演算に親和性が高いか」で決まることになる。例えば8×8の演算なら高速だが、9×9などではいきなり効率が4分の1に落ちることになりかねない

最大512回というあたりだとすると、例えば2次元行列乗算なら16×16の行列(データ型8bit)同士の乗算の合計をCに出力とか、3次元テンソルなら8×8×8の行列の乗算を実行できる格好になる。従来のプロセッサーでは、このためには2次元なら最低でも(演算命令+データ移動命令)×256、3次元なら×512個が必要なので、これを1命令で済ませられることの効果は大きい。

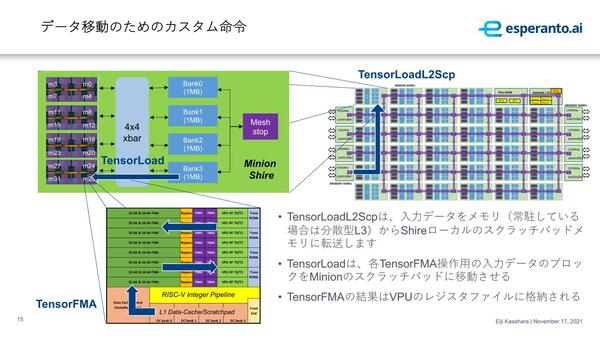

ただ命令実行の方は自動でできるとして、問題になるのはデータのロード/セーブである。なにしろ最大だと1命令で32K演算なので、Int 8としても32KB分のロードとセーブが512サイクルごとに入ることになる。

もっと正確に言えば、レジスターファイルが512個並んでいれば512サイクルごとに入れ替えれば済むことになるが、実際にはそんな巨大なレジスターファイルを置くのはエリアサイズ的にも消費電力的にも無理である。

データ移動の構図。外部メモリーから内部の2Dメッシュ経由で読みだされ、一旦Shire内のSRAMに格納。ここからTensorLoad経由で個々のET-Minionの1次データキャッシュに入り、そこからレジスターファイルにロードされる。この際、外部メモリーアドレスを自動的にインクリメントする、それこそDMAコントローラー的な機能がどこかに入っているものと思われる

したがってレジスターファイルと1次データキャッシュの間で常にデータのやり取りが発生する格好になる(しかもこれはET-Minionのロード/ストアー命令ではなく、テンソル命令を発行するとロード/ストアーユニットが(RISC-Vのパイプラインとは独立に)動作して、定期的にデータのロード/セーブをSRAMとの間で行なう形になる。レジスターファイルは8組なので、例えば4組ごとにロード/セーブをするのかもしれない。

これが理想的に動作すれば、1個のET-Mineonで32FLOPs/サイクル、これが1088個同時動作で34816FLOPs/サイクルである。300MHz動作なら1044GLOPSs相当になるわけで、「100~1000TOPSのピークレート」を1個のET-SoC-1で実現できるわけだ。

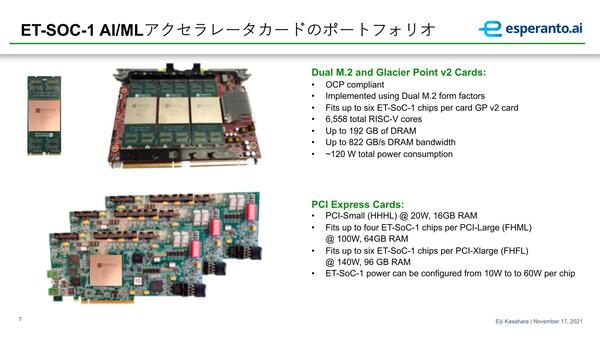

デュアルM.2カードとPCIeカードに

ET-SoC-1が搭載される

なお、ET-SoC-1は、デュアルM.2カードとPCIeカードの2種類の形で提供される予定だそうだ。

さらにデータセンター向けとしては、そのGP v2カードを2つ搭載したYosemite v2 Sledや、それをさらに4つ搭載したYosemite v2 Cubby、そのCubbiyを8つ搭載したラック構成なども想定されているとする。

CP GP v2カードで120W、Yosemite v2 Sledで240W、Yosemite v2 Cubbyで960W、ラック全体では8KWといったところ。ただYosemite v2 Sled以降は相互接続用ネットワーク(100Gイーサネットあたり)の分も加味しないといけないので、もう少し消費電力は増えそうだ

すでにCelebresやGraphcoreのように、サーバー向けに先行者利益を享受しているベンダーもある中で、今後Espelantoがどれだけ巻き返しを図れるのか、楽しみである。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ