前回は細かい話を全部飛ばして、大枠での説明だったので、今回からもう少し細かく説明していきたい。まず今回はAlder Lakeに関する話だ。

さて、HotChipsでは、Alder Lake自身やそのコンポーネントであるP-Core/E-Coreに関する詳細はほとんど説明がなく、唯一Thread Directorに関してのみ突っ込んだ話があった。したがって、主にArchitecture Dayのスライドを使いつつ、要所のみHotChipsでのスライドを使いながらご紹介説明したい。

第12世代デスクトップ向けマイクロプロセッサー

Alder Lake

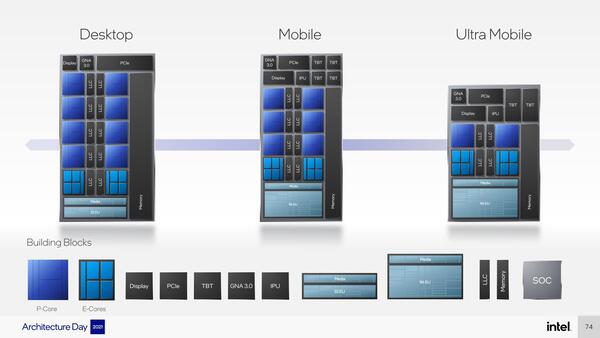

Alder Lakeの構成そのものは前回も紹介した。下の画像はデスクトップ構成のものだが、最大16コアで、P-Core×8、E-Core×8である。ただハイパースレッディングはP-Coreのみ有効とされ、E-Coreはハイパースレッディング無効の状態で実装される。つまり、システム全体としては最大24スレッドになる。

もう1つおもしろいのはLLCが最大30MBになったこと。前回掲載したAlder Lakeの構成図にもあるように、それぞれのP-Coreと、4コアのE-Coreクラスターにそれぞれ1つづつのLLCが組み合わされる形となるので、LLCそのものは1個3MBになる。

ちなみにこのLLCはP-CoreとE-Core、およびGPUからもアクセス可能になっており、システム全体で共有できるという話であった。

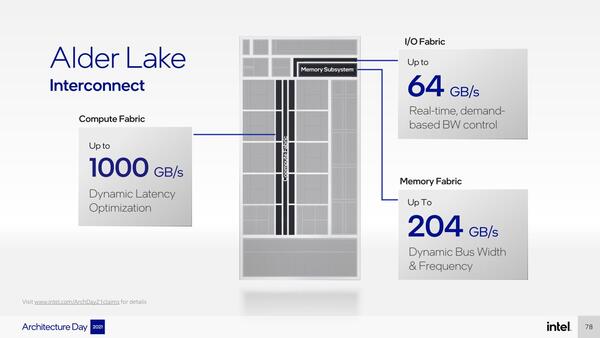

次にインターコネクト。内部のインターコネクトは最大1000GB/秒にも達する。I/O Fabricの64GB/秒というのは、前回のPCIe構成図で説明したようにPCIe Gen5 x16レーンが出るからである。

PCIe Gen5は転送速度が32GT/秒なので1レーンあたり4GB/秒、x16レーンで64GB/秒という計算である。もっとも現状、まだPCIe Gen5対応GPUが存在していない以上、やや宝の持ち腐れ感はある。ちなみにPCHとの接続が、DMI 4.0ベースなのか、DMI 3.0×2構成なのかはまだはっきりしない。

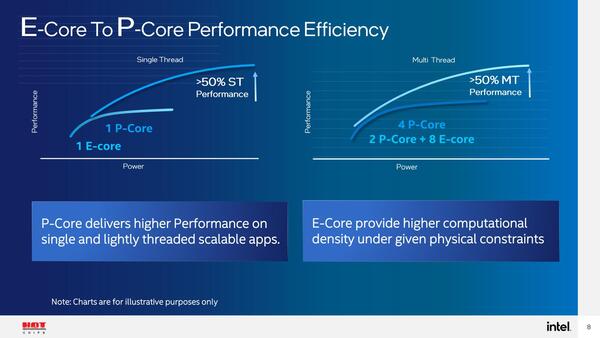

さて、Alder LakeではP-CoreとE-Coreが載るわけだが、Architecture DayではE-CoreはSkylakeとの比較、P-CoreはCypress Cove(Rocke Lake)との比較で、今ひとつ全体としての性能がわからなかった。今回HotChipsではE-CoreとP-Coreの性能比較が示された。

これを一見してわかるのは、予想以上にE-Coreが省電力方向に振っていることだ。この後説明するが、E-CoreはTremontと比べてもかなりゴージャスというか、そもそもSkylakeと比較してもIPCが高めとされていたし、それそのものは事実だろう。実際バックエンド側はSkylakeを超える規模になっているから、IPCが向上していることそのものは不思議ではないが、普通にこれを実装すれば、Skylakeと同等以上のエリアサイズになる。

ところが実際E-CoreはP-Coreよりもずっと小さい。まだダイサイズの写真などが公開されていないので正確なところは不明だが、本記事冒頭の図ではE-CoreはP-Coreの1/4以下の面積でしかない。もちろんこれは正確な比率ではないと思うが、Mobile/Ultra Mobileでは1つのP-Coreをほぼ4つのE-Coreで置き換えている形になっていることを考えると、相当小さいことは間違いない。

回路規模が相応に大きく省電力で動き、しかもプロセスそのものはP-Core同様にIntel 7が利用されるという話であれば、実装としては以下のあたりが思いつく。

- 利用するトランジスタの種類が、高密度・省電力向けのものを使っている

- パイプラインの一つのステージに、かなり多くの回路を突っ込んでいる

トランジスタの種類を変えられるのか? と言われそうだが、例えばFinFETの構造そのものは同じであっても高速回路向けにはFinの数を増やして駆動電流を増やすのが一般的なので、逆に1Finだけで構築すれば動作速度は落ちるものの消費電力は減るし、エリアサイズも削減できる。

ただこうした結果として、E-Coreのベストな性能はP-Core最低動作周波数程度に落ち着くことになる。おもしろいのは、P-Coreでマルチスレッド性能を追求しようとするとどうしても動作周波数を上げざるを得ないし、そうなると効率は急速に落ちる。逆にE-Coreを大量に動かしても、動作周波数を低めに抑えることで消費電力はそれほど上がらないため、マルチスレッド系の処理性能効率は上がるというわけだ。なかなかおもしろい特性である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ