ロードマップでわかる!当世プロセッサー事情 第629回

Intel Architecture Day 2021で発表された11のテーマ インテル CPUロードマップ

2021年08月23日 12時00分更新

日本時間の8月19日、Intel Architecture Day 2021がオンラインで公開になった。その内容はこのページのほか、YouTubeでも視聴可能だ。ちなみに全部で2時間16分にもおよぶ長大なセッションで、11ものテーマについて説明があった。

今回はこの概要のみを説明したい。なぜ概要かというと、1つは個別に細かい説明をしていると文量が多すぎること、もう1つはこの後にもっと細かい説明が予定されているためだ。米国時間で8月22日より、IEEEのHotChips 33がオンラインで開催されるが、ここで以下の4つのセッションが予定されている。

| HotChips 33で予定されているセッション | ||||||

|---|---|---|---|---|---|---|

| セッション | 登壇者 | |||||

| Intel Alder Lake CPU Architectures | Efraim Rotem氏 | |||||

| Next-Gen Intel Xeon CPU - Sapphire Rapids | Arijit Biswas氏およびSailesh Kottapalli氏 | |||||

| Intel's Hyperscale-Ready SmartNIC for Infrastructure Processing | Bradley Burres氏 | |||||

| Intel's Ponte Vecchio GPU Architecture | David Blythe氏 | |||||

またこれとは別にチュートリアルセッションでRavi Mahajan氏とSandeep Sane氏による“Case Study: Intel products built with 2.5D and 3D packaging”が予定されている。そこで個々の詳細はHotChipsでの内容を踏まえたうえで説明することとし、とりあえずは概要だけを説明することにしたい。

さて、まず11のテーマ内容をかいつまんで説明する。文量の関係でMount Evansは後送りとさせていただき、今回はXe HPC&Ponte Vecchioまでを説明する。

| Intel Architecture Day 2021で説明があった11のテーマ | ||||||

|---|---|---|---|---|---|---|

| テーマ | 内容 | |||||

| Performance Core(P-Core) | かつてGolden Coveとして呼ばれていたコア。Tiger Lakeに実装されるWillow Coveの後継。Alder Lake及びSapphire Rapidsに搭載される。 | |||||

| Efficient Core(E-Core) | かつてGlacemontと呼ばれていたコア。Lakefieldに搭載されていたTremontの後継。Alder Lakeに搭載される。 | |||||

| Intel Thread Director | Alder LakeでP-CoreとE-Coreのスケジューリングを助けるコア。big.LITTlEをサポートする。 | |||||

| Alder Lake | P-CoreとE-Coreの両方を搭載する、コンシューマ向けプロセッサー。Intel Thread Directorも活用される。AMXは非搭載。 | |||||

| AMX | これは連載569回で説明したAMX拡張命令周りの話。Sapphire Lapidsに搭載される。 | |||||

| Sapphire Rapids | P-Coreを実装するXeon向けプロセッサー。AMXは搭載する一方。Intel Thread Directorは未搭載。 | |||||

| Xe Core | Xe HPC/Xe HPGで利用されるXeの基本単位。 | |||||

| Xe HPG | 先日Intel ARCというブランド名が発表された、インテルのディスクリート・グラフィックス第2弾。 | |||||

| XeSS | Xe HPG上で利用可能なSuper Sampling技法。 | |||||

| Xe HPC&Ponte Vecchio | HPC向けGPU。 | |||||

| Mount Evans | 次世代IPU(Infrastructure Processing Unit)。 | |||||

Efficient Core(E-Core)

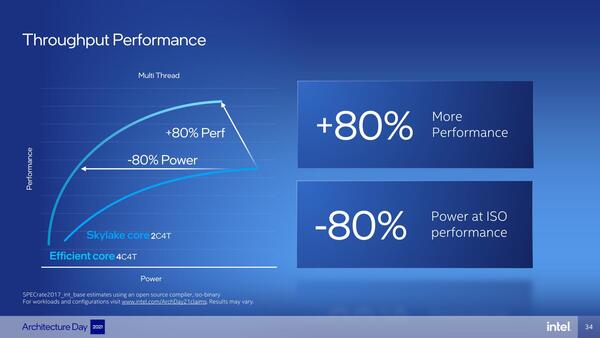

こちらはTremontコアの後継ということもあり、基本的な構造はTremontによく似ている。ただフロントエンドはよく似ているが、バックエンドは猛烈に拡充されており、もうこれだけ見ていればP-Coreと大差ないのでは? という気になる。

細かい内部構造は後日Alder Lakeのところで説明するが、シングルスレッド性能はSkylake比で40%向上、Multi Thread性能は80%向上すると説明されている。

Performance Core(P-Core)

こちらは以前のロードマップではWillow Coveと説明されていたコアだ。P-CoreはSunny Cove/Willow Coveの延長にあるが、ついにALUが5つに増量され、またLoad/Storeユニットが合計7つというお化け構成になった。

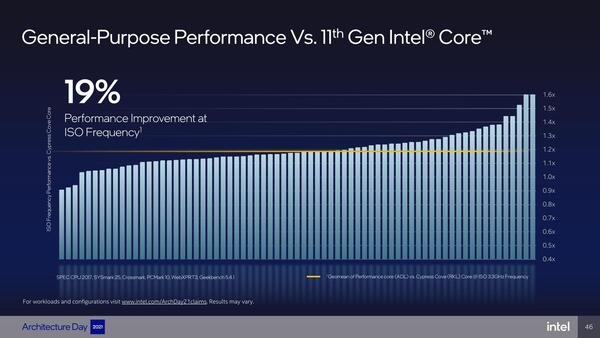

こちらであるが、Rocket Cypress Cove(つまりSunny Coveの14nm版)と比較して、平均で19%のIPC向上が実現された、としている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 - この連載の一覧へ