ロードマップでわかる!当世プロセッサー事情 第618回

COMPUTEXで発表した積層技術3D V-Cacheは性能向上と歩留まりを改善する新兵器 AMD CPUロードマップ

2021年06月07日 12時00分更新

V-Cacheのおかげで歩留まりが改善し性能も向上する

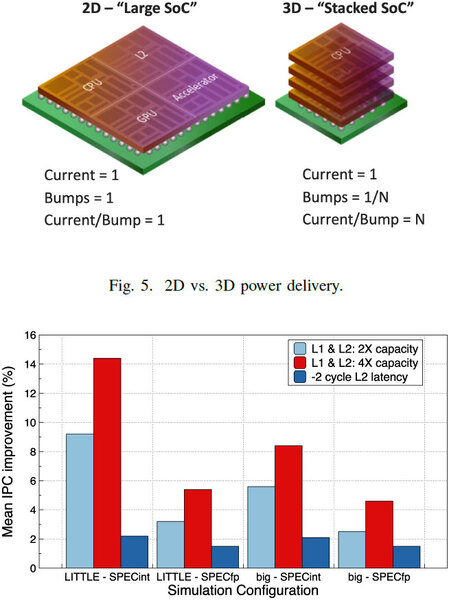

V-Cacheによるメリットは多い。まず最初は純粋に性能向上である。加藤勝明氏の記事にあるように、ゲームで平均15%のフレームレート向上があったとするが、実はこれ以外にもArmが2020年に出した“Stack up your chips: Betting on 3D integration to augment Moores Law scaling”という論文が興味深い。

これはArmのSoCを積層構成にして、その際に1次/2次キャッシュの容量を増やすとどう性能が変わるのかを論じたものだが、下の画像のグラフで示すように、bigコア/LITTLEコアや整数演算/浮動小数点演算で差があるものの、IPCが2~14%向上することが示されている。今回の場合は3次キャッシュなので直接この結果が適用できるわけではないが、わりとおもしろい結果である。

2つ目は製品の歩留まりを改善できることだ。仮に同じ容量を積層技術を使わずに実現すると、CCDのサイズは150mm2を超えることになり、当然製品の歩留まりが落ちる。ところが3次元積層では、CCDとV-Cache×2を別々に製造しておき、まず不良品を撥ねて良品のみで積層できるため、結果的に歩留まりが大幅に上がることになる。少なくとも現在のZen 3よりも歩留まりが下がることはないのは大きなメリットだろう。

3つ目は製品ラインナップを増やす余地があることだ。先の話ではないが、V-Cacheなし(32MB L3)/1枚(64MB L3)/2枚(96MB L3)/4枚(160MB L3)といろいろバリエーションを用意できる。しかもそれを後工程で実現できるのは、製品展開の幅を広げることにつながる。

また今回はZen 3コア(最初のターゲットはEPYC向けだろう)だが、将来的には例えば次のRyzen G(コード名はRembrantらしい)や、その次(コード名はPhoenixだそうだ)の場合、L3兼インフィニティーキャッシュとして積層することで、大幅にGPU性能を引き上げ可能になるだろう。

あるいはNAVI系列についても、Radeon RX 6900 XTクラスはすでにインフィニティーキャッシュがやや不足気味で、特に4Kをフルにぶん回すとGeForce RTX 3090に追従しきれないシーンが見られたが、インフィニティーキャッシュにこれを応用して、例えば256MBなどに増量すればさらに性能が向上するだろう。

これまでダイサイズ肥大化を避けるためにギリギリで構成されていたキャッシュの容量を大幅に引き上げることで、絶対性能あるいは性能/消費電力比を引き上げるという新たな武器をAMDは手に入れたわけだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ