ロードマップでわかる!当世プロセッサー事情 第618回

COMPUTEXで発表した積層技術3D V-Cacheは性能向上と歩留まりを改善する新兵器 AMD CPUロードマップ

2021年06月07日 12時00分更新

進化していく3次元積層技術

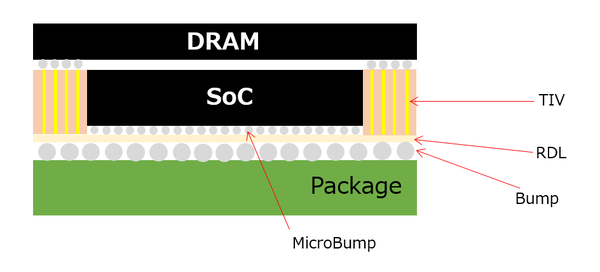

CoWoSに続く第2世代がInFO(Integrated Fan-Out)である。こちらはPC向けにはあまり利用されず、主にスマートフォンなどのモバイル機器向けのものだ。InFOを最初に採用したのがアップルという噂があるが公式には未公表である。構造は下図のようになる。

SoCの上にDRAMを積層する、今度こそ真の3D構成になったわけだ。この方式では、従来と同じチップの作り方をしながら3D積層が可能になる。ただしSoCの上にDRAMが配されることになるので、あまりSoCの消費電力が多い(=発熱が多い)とDRAMが安定稼働しなくなる。その意味ではモバイル機器など消費電力の低いSoCでないと使いにくい技術である。

まずSoCからの配線はRDL(Re-Distribution Layer:再配線層)にMicroBumpで接続される。このRDL、構造的にはCoWoSのシリコン基板に近いが、次に出てくるTIVと接続するために若干違うものになっている。

さて、外部へのピンや電源/GNDなどはそのままRDL経由で一番下のBumpを経てパッケージに接続される格好だが、DRAMへの配線はRDLの両端に立てられたTIV(Through InFO Via)と呼ばれる縦方向の配線につながる。このTIVの反対側はDRAMチップの端子につながるという構造だ。

なお、図ではDRAMのサイズにRDLを合わせているが、RDLをもう少し大きくすれば、積層数をさらに引き上げることもできる。実際TSMCは2017年のSymposium on VLSI TechnologyでこのInFOを発表したが、その際には4つのチップをInFOを使って積層した場合の構成を紹介している。

InFOも今はさらに発展し、図の構成のInFO_PoP(Package on Package)の他に、5Gアプリケーションなどに向けてより配線密度を上げたInFO_oS(InFO on Substrate)も登場している。

ちなみにこのInFOに相当するインテルの技術がFoverosと目されている。インテルはFoverosに関してあまり細かい話を説明していないが、機能的に見ればほぼInFoに近いとみられる。ただしInFOとは逆に、むしろ省電力でサイズの大きなチップを下に置く形になっている。

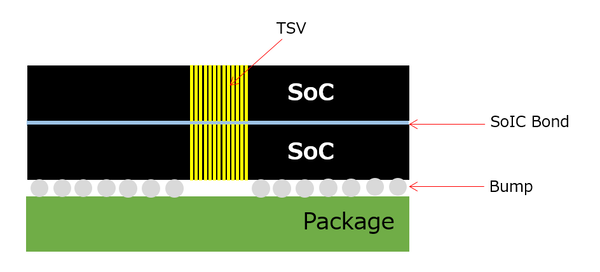

ということで、いよいよ第3世代であるSoICだ。ここまでの世代は、SoCには手を入れない(もちろんMicroBumpへの対応などはあるので、まるっきり既製品のままというわけにはいかないが)形での3D積層を模索していたが、この第3世代ではチップ内にTSV(Through Silicon Via:シリコン貫通電極)を実装することで、チップの真上にチップを積層することを可能にする技術である。

もともとTSVそのものは以前からずっと実用に向けて研究開発が進んでいたが、どうしても高コストになるということでなかなか普及しなかった。TSVを埋め込むのにも、正確に位置合わせして2つのチップを張り合わせるのにも高度な技術が必要であり、歩留まりもそれほど良くなかったからだ。

ただDRAMの世界ではDDR4世代で3DS(3D Stacking)やHBM/HBM2など、内部的にはTSVを利用した製品は量産されており、これをどのタイミングでロジックに持ってくるのかという感じであったが、TSMCが先鞭をつけた格好だ。

構造そのものは下図のようになる。SoCにTSVを埋め込み、ここで2つのチップ間の通信をする仕組みである。外部との接続は、一番下のSoCに通常のBumpが配されており、これ経由ということになる。

ここで肝になるのが、2つのSoCをどうつなげるかという話だが、TSMCの論文によればSoIC Bondなる謎の接続技術が開発されており、これを利用することで可能になったとする。本当に接着剤の類ではないとは思うのだが、ここがノウハウの部分だけにTSMCも今のところ詳細は説明していない。

ただTSMCによれば、このSoIC Bondはキャパシタ(静電容量)がほぼゼロに近いとされ、このためCoWoSなどに比べてもずっと効率が良いとされる。論文によればCoWoSと、従来考えられていたTSV+MicroBump、それと今回のSoICを比較した場合の特性は下のようになるとする。

| 3次元積層技術の特性 | ||||||

|---|---|---|---|---|---|---|

| CoWoS | TSV+MicroBump | SoIC | ||||

| 配線密度 | 0.8x | 1.0x | 16.0x | |||

| 転送速度 | 0.01x | 0.1x~1.0x | 3.7x~11.9x | |||

| 消費電力 | 22.9x | 1.0x~3.7x | 0.05x~0.6x | |||

ここでTSV+MicroBump、およびSoICで幅があるのは、チップの表面同士をつなげるか、表裏でつなげるかで差が出てくるからで、数値の基準はチップ表面同士の接続となるTSV+MicroBumpで、これを1.0倍とした際の数字となっている。

SoICは、従来考えられていたTSVと比較しても16倍の配線密度と4~12倍の転送速度を実現しつつ、1bitを転送するのに必要な消費電力は0.05~0.6倍と極めて低くなっている。

ちなみに、インテルはまだこれに相当する技術を明らかにしていない。強いて言えばFoverosがそれに該当するのかもしれないが、このあたりはインテルがもう少しFoverosの技術的な要素を公開してくれないと判断できない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ