ロードマップでわかる!当世プロセッサー事情 第618回

COMPUTEXで発表した積層技術3D V-Cacheは性能向上と歩留まりを改善する新兵器 AMD CPUロードマップ

2021年06月07日 12時00分更新

3D V-Cacheによる積層で

キャッシュ容量を大幅に増量できる

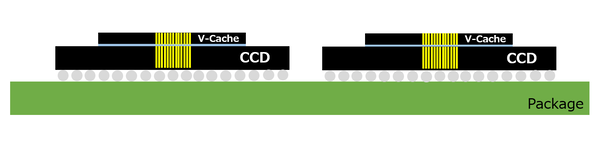

だいぶ3次元積層技術の話が長くなってしまったが、話を3D V-Cacheに戻す。今回はRyzen 9 5900Xを利用したプロトタイプなので、構造は下図のようになる。2つのCCDの上に、64MBのV-Cacheが載り、これも3次キャッシュ(以下、L3)として利用できるので、プログラムから見るとL3が96MBに増えたように見える構造だ。

実は基調講演終了後に、このV-Cacheに関してTwitterで多数のメンションが飛びまくった。中にいくつか「AMDからの返答をもらった」というものがあったので、筆者も直接「こういうメンションがTwitterで飛んでいるが事実か?」をAMDの広報に確認をして返事をいただいている。それによって以下のことが公式に確認された。

- V-Cacheの構成は1層。容量は64MB。

- V-Cache構成とすることの、放熱に関する影響は軽微である。他の3次元積層の方式と比較しても圧倒的に優れており、従来の2Dシリコンそのままとほとんど差がない。

- V-Cacheのレイテンシーは、CCD上のL3アクセスよりもわずかに増える。ただ一般論としてキャッシュサイズが増えればどうしてもレイテンシーは大きくなり、これはV-Cacheも例外ではない。ただ、64MBのL3増加にともなうDRAMアクセス頻度の低下を考えれば、V-Cacheのレイテンシー増加は問題にならない程度と考えられる。

- V-Cacheの消費電力は大きな影響はない。

- CCDはV-Cacheを積む関係で、薄型化されている。

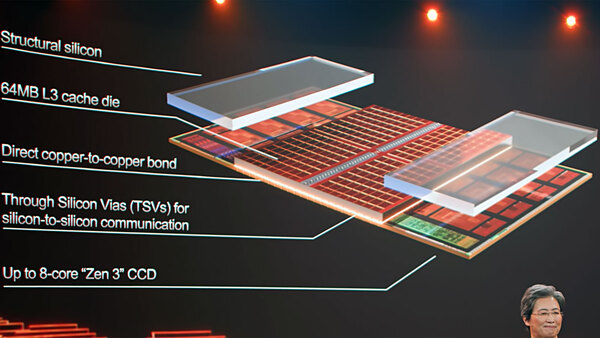

これをベースにもう少し構成を解説しよう。まず容量の件。下の画像は基調講演における構造図であるが、“64MB L3 cache die”はどう見てももともとのCCDの半分程度の面積しかない。

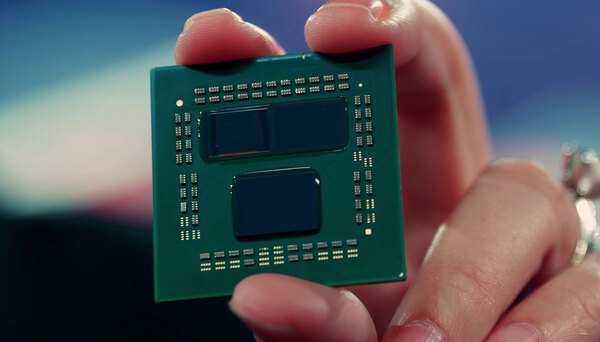

実際Su CEO自ら「6×6mmのSRAMをCCDの上に載せている」と明言しており、フットプリントは36mm2ということになる。この数字は丸めていると思うので、多少誤差はあるだろう。Zen 3のダイサイズはおおむね80mm2とされるから、ざっくり半分といったところだ。

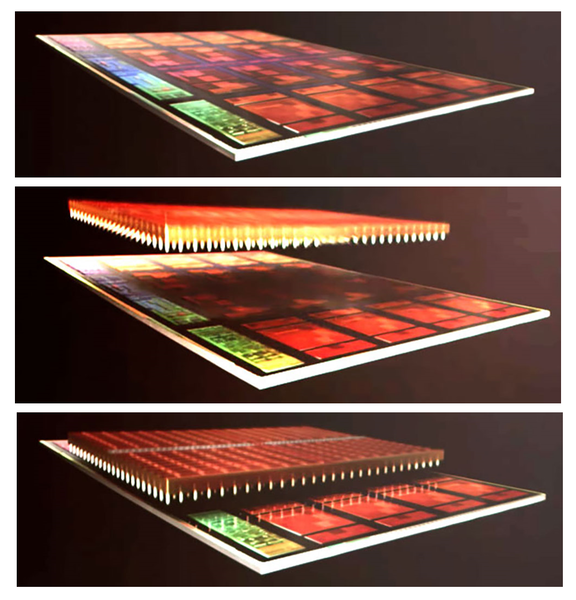

さて、Zen 3のCCDそのものも、もともと半分くらいの面積をL3に充てていた(下の画像上段)。V-Cacheは、横幅に関してはほぼCCDのL3と同程度で、ただし縦方向はL3+Zen 3コアをはみ出して、インフィニティーファブリックのI/F部あたりまではみ出しているようになっている(下の画像中段)。

ちなみにこの画像ではV-Cacheの全面にTSVが出ているように描画されているが、これは単なる映像効果であって、実際にはこんなに出ていないだろう(上の画像下段)。

問題は「どうやって36mm2に64MB SRAMを押し込めるか」である。CCDのダイ上のL3面積は、画像からもわかるようにおおむね36mm2で32MB SRAMしか構成できない。そもそもSRAMは一番面積を喰うロジック回路であって、MLC NANDフラッシュのように1つのSRAMセルで2bitを記憶する方法がない以上、倍密度にする方法はなかった。

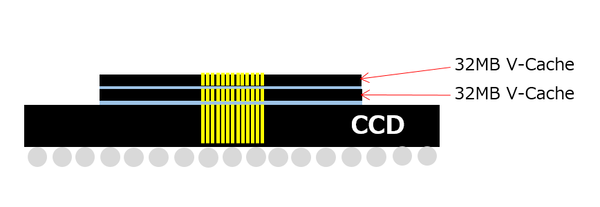

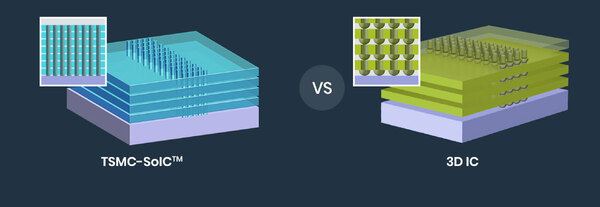

ではこれをどう解決したか?であるが、下図のように32MBのチップを2枚重ねればいい。そしてこの2枚重ねたものを「1層の64MB V-Cache」とAMDは言い張っているのだと思われる。そもそもSoIC自体、3枚以上のチップを積み重ねることを想定しており、こうした構成は難しくないと思われる。

TSMCの“The Whats, Whys, and Hows of TSMC-SoIC”というページに掲載されたインフォグラムから抜粋。ベースとなるチップの上に4枚のロジックチップが積層されているのがわかる

実はこれ、傍証もある。Andreas Schilling氏の6月1日のメンションによれば、AMDのDaytona Platform(第2世代EPYC向けのサーバー向けプラットフォーム)にMilan(第3世代EPYC)対応BIOSをインストールすると、BIOS セットアップにX3Dという項目が出現し、最大4スタックまでの構成が選べるようになるそうだ。

Its always good to have a Daytona platform server at hand ?? https://t.co/wdbCzsHMNHpic.twitter.com/JHjocLN6jP

— Andreas Schilling (@aschilling) June 1, 2021

氏のツイートが本当であるとすれば(これは今のところ確証はない)おろらくこれがV-Cacheで、32MBが1スタック、64MBが2スタック、128MBが4スタックになると思われる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ