ロードマップでわかる!当世プロセッサー事情 第610回

Ice Lake-SPが発表、前世代より大幅に性能が向上したというが…… インテル CPUロードマップ

2021年04月12日 12時00分更新

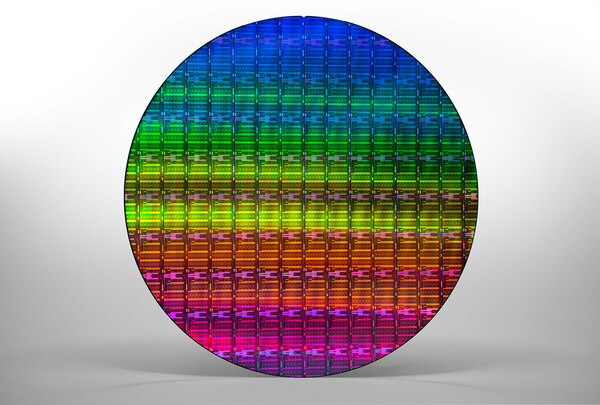

Ice Lake-SPのは1枚ウェハーから

84ダイが取れる

この後もう少し発表会の内容をご紹介するが、その前に連載607回の答え合わせをしたい。筆者は28コアのIce Lake-SPのダイサイズがおおよそ660mm2ちかくなると予測したが、実際にウェハー写真が公開された。

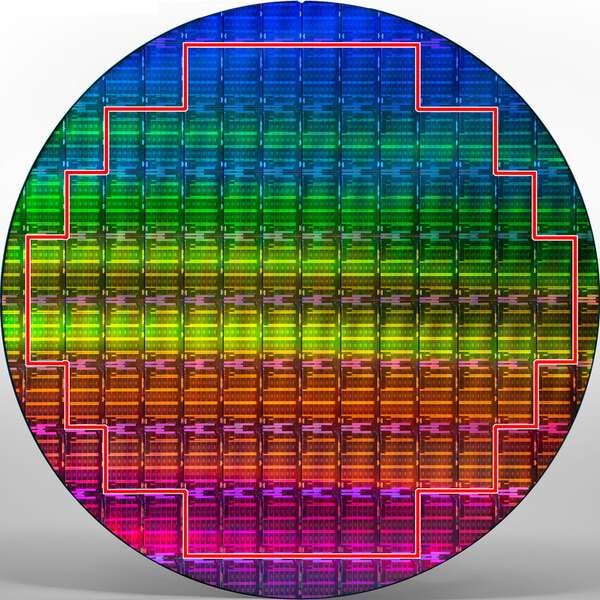

これの歪みを取って、真円になるように変形した結果が下の画像で、合計で84ダイが取れることが判明した。またダイ1個あたりの寸法も、おおよそ19.7mm×32.3mmで、634.3mm2ほどになる。

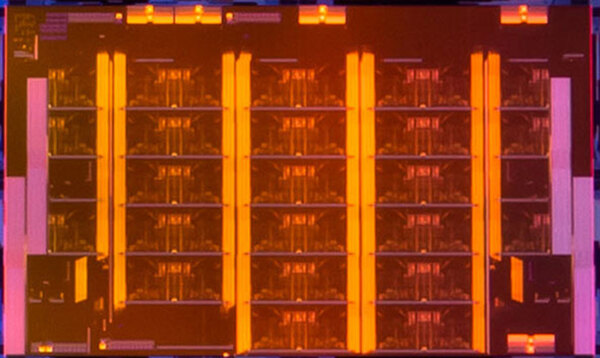

そのダイの一つを拡大したのが下の画像であるが、昨年のHotChipsで公開されたレイアウト図と合わない。

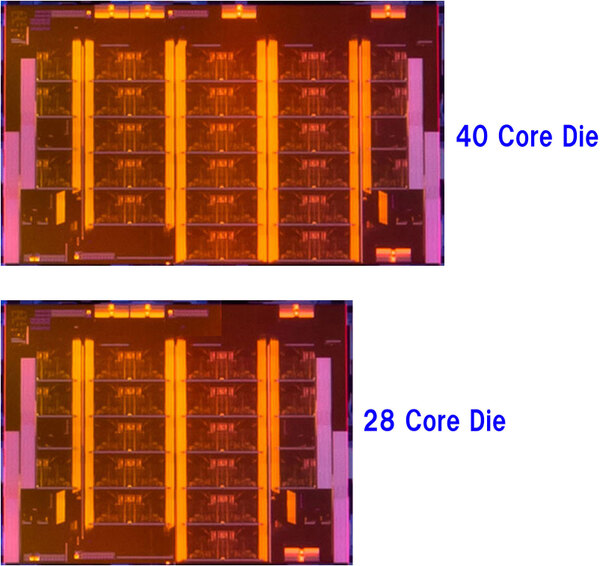

そこでレイアウトをきちんと入れてみたのが下の画像だ。実はこの634.3mm2のダイは40コアの製品であった。

では28ダイだとどうなるか? を推定したのが下の画像で、横幅がおよそ25.6mm(高さは19.7mmのまま)、ダイサイズは504.3mm2ほどになる。

残念ながらインテルはCascade Lake/Cooper Lakeのダイやウェハーを公開していない関係でサイズの比較が難しいのだが、ラフに言って40コアのIce Lake-SPと28コアのCascade Lake-SP/Cooper Lakeが同等レベルと考えると、確かにプロセス微細化の効果があったことになる。

ただ40コアで630mm2というダイサイズは結構大きい。以前連載596回で56コア構成の推定をしたが、仮にこの構成だとするとダイサイズは950mm2前後になる。

さすがにこれは大きすぎるように思う。もう2019年8月にCooper Lakeを発表した際の公約はどっかに行ってしまった可能性が大であり、Sapphire Rapidsまで56コア/ソケットの実現はお預けになる、と考えるのが一番妥当そうだ。

ついでにそのSapphire Rapidsについて。まだ詳細な情報は出てきていないのだが、連載586回でご紹介した、ADOREDTVが公開した内部構成の概略を裏付けるような話がチラチラ出ている辺り、本当にこういう構成になるのかもしれない。追加情報としては以下の話が出てきた程度である。

- TDPはローエンドが225W、メインストリームが270W、ハイエンドが350W

- ハイエンドは56コア。他に(少なくとも)24/44コアの製品もある。

- PCIeはPCIe Gen5/CXLが最大80レーンのほか、PCIe Gen4がx2レーン用意される(PCH接続用だろうか?)

またサーバー向けのSapphire Rapids-SP以外に、ハイエンドデスクトップ(Core-X向け?)のSapphire Rapids-Xも用意されるという話もある。製造プロセスは10nm Enhanced SuperFinで、順調ならTSMCの7nmと同程度の動作周波数まで引き上げられることになるのだが、このあたりはもう実物が出るまでなんとも言えない。

以前のロードマップによれば、2021年中に投入予定であるが、すでにIce Lake-SPがずれているだけに、Sapphire Rapidsがどこまで順調にリリースされるかは未知数である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ