自動車向けAIチップの市場で成功

1000万個のチップの出荷を記録

自動運転向けAIプロセッサーの成果が、2018年のCESで発表されたv-MP6000UDXである。コンセプトは簡単で、自動運転に必要となるさまざまな処理のうち、純粋に画像処理が必要な部分は従来の機能で、認識や判断が必要な部分をAIで処理する仕組みである。

v-MP6000UDXのコンセプト。問題はvideantisのソリューションは画像をメインにしていることで、昨今のLADERやLiDARを組み合わせたSensor Fusionをどう取り扱うのかが見えないところ。このあたりは次世代製品送りになるのかもしれない

v-MP6000UDXのコアそのものは既存のv-MP4000HDXシリーズの延長にあり、最大256コアまでできるという、いわば力業である。

コアそのものはv-SP(v-2000SPの延長と思われる)と、v-MP(v-2000MPの拡張版)から構成されるという構図は同じであり、主な変更点はそのv-MPに畳み込みニューラルネットワーク向けのアクセラレーターを追加したことである。

問題はこの図に畳み込みニューラルネットワーク向けのアクセラレーターが記載されていないこと。Dual-issue VLIW/SIMDとあるあたり、おそらくVector exec unitの中にアクセラレーターが統合されている(Vector exec Unitを改造して8bit×64あるいは16bit×32の演算を可能にした)ものと思われる

8bitで64MAC/サイクルなので、仮に256コアでは16384MAC/サイクルとなる。CentaurのAVX-32768も真っ青な性能である(256コアだと131072bitを同時に処理できるからだ)。さすがにこれは理論上可能というだけで、実際はもっと少ない。後述の例では16コアあたりがリーズナブルな構成とみなされているようだ。

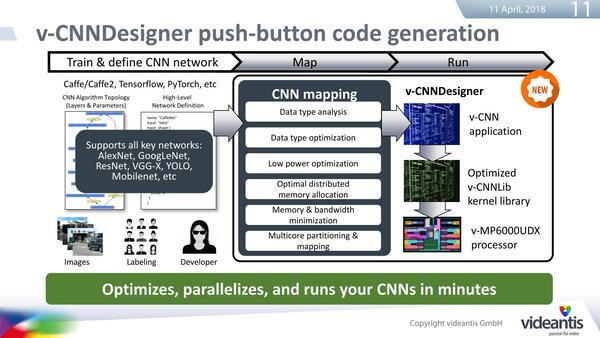

ソフトウェアについては、主要なネットワークのフレームワークをv-MP用に変更する、畳み込みニューラルネットワークのマッピング用ソフトがv-CNNDesignerとして提供され、これを利用して実行させることになる。

実際いくつかの例が示されているが、16コア程度のv-MP6000UDXで無理なく処理ができているとする。

もちろんこれでいきなりLevel 4の自動運転をしろというのは無理であるが、こちらはまだそもそもアルゴリズムが確立できていないし、必要ならさらにコア数を増やすことで演算性能は上げられるので、機能的に足りないわけではないだろう。

拠点をドイツに置いていることもあり、早くから自動車業界に食い込んでいたというアドバンテージもあって、2019年にはKI-FLEXという自動運転チップに採用され、今年2月15日には1000万個のチップの出荷を記録したというあたり、videantisはうまく顧客をつかんで自動車向けAIチップの市場で存在感を出している。

アーキテクチャー的にはそれほど凝ったものではないのだが、むしろそれが(ある意味保守的な自動車業界向けとして)功を奏しているのかもしれない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ