フラッシュメモリーを流用して

Analog Computerに仕立て上げる

もう1つは、データは移動してナンボという話である。自分の計算結果をそのまま次の演算で使う場合には、この方式は極めて効率が良い。ところが、それこそAI推論のように毎サイクル異なるデータの演算を行なう場合、結果としてデータのメモリー間移動が発生することは避けられない。つまり

メモリー→キャッシュ→レジスター→演算器→(計算)→レジスター→キャッシュ→メモリー

という流れが、以下に削減されるだけである。

メモリー→キャッシュ→演算セル→(計算)→キャッシュ→メモリー

この場合、メモリー→キャッシュやキャッシュ→レジスターあるいは演算セルのデータ移動の消費電力がはるかに大きいので、レジスターを減らすことで消費電力を多少減らせるとしても、それほど大きいものではない。

少なくともIn-Memory Computingを採用することで複雑化する内部構造や演算の制約などのデメリットに見合うだけの消費電力削減効果は期待できないということだ。

これをMythicはどうしたか? という話はあとに回すとして、最大のポイントがAnalog Computingである。Mythicは2018年のHot Chips 30において“Analog Computation in Flash Memory for Datacenter-scale AI Inference in a Small Chip”という講演を行なっているが、彼らのアイディアは2次元構造にしたフラッシュメモリーを流用して、そのままこれをAnalog Computerに仕立て上げるというものだ。

以前V-NANDの解説に絡んでフラッシュメモリーの構造を解説したことがあるが、Floating Gateと呼ばれる領域に電荷をため込むことで、これをメモリーセルとして利用する方式である。

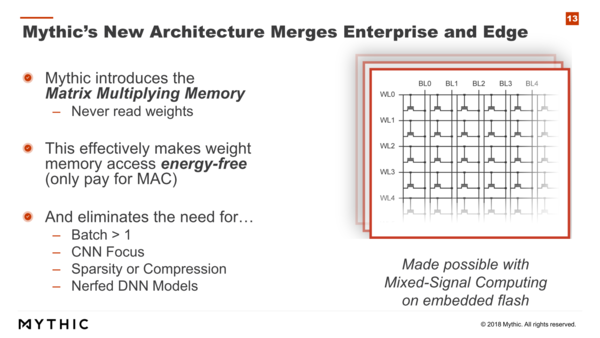

構造そのものは、WL(Word Line)とBL(Bit Line)の交点にFloating Gateのセルを1つずつ置く形である。このセルに、ネットワークの重みをあらかじめロードしておく。つまりこのMatrix Multiplying Memoryと呼ばれるものは、これそのものがネットワークの重みを格納できるメモリーになるわけだ。

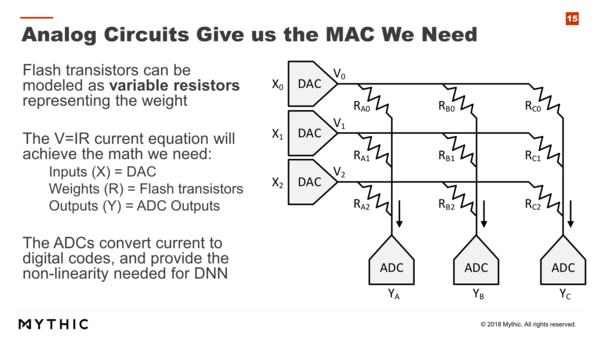

さて、このセルは可変抵抗として扱える。セルとはいっても構造的にはMOSFETであり、MOSFETはVds(ドレイン/ソース間電圧)がVgs-Vth(ゲート/ソース間電圧-閾値電圧)より低い間は、線形の抵抗として機能する。すると、オームの法則(電圧=電流×抵抗)を変形させて(電流=電圧÷抵抗)利用して乗算と加算ができることになる。

入力データはDAC(Digital Analog Converter)を利用して値を電圧に変換して、Matrix Multiplying Memoryにかけてやると、それぞれのメモリーセルの値の逆数に比例する電流が斜め方向に流れることになる。これが乗算だ。

そして最終的にADCで受けるのは、複数のセルから流れてきた電流の合計値であるから、ここで加算ができることになる。

DAC/ADCに関してもやはり8bit程度の精度が必要になるため、これがそれなりの面積を喰うが、M1108に関してはDACではなくデジタルの近似回路を利用しており、将来のバージョンではここもちゃんとDACにする予定という話であった

ここで問題になるのはR、つまり個々のメモリーセルを利用した抵抗の精度である。SLCだと0か1の1bit、MLC/TLC/QLCでもそれぞれ2/3/4bitだから、最大でも16レベルでしかない。ただこれはMLC/TLC/QLCと同じく、継ぎ足しを行なえばもっと多値化が可能になる。

実際Mythicでは8bit演算を可能にしているから256レベルの値を保持できることになる。もっともさすがにこれを1個のメモリーセルで実現するのは難しいので、Mythicでは2つのメモリーセルをペアにし、2つのセルの値の差で-128~+128までを保持するようにしている。

こういうことをするとメモリーセルの寿命が気になるかもしれないが、フラッシュメモリーそのものと違い、そもそも書き込みを煩雑におこなったりする使い方ではない。端的に言えば、あるネットワークをロードするときに1回、それぞれのWeightをロードしたら、別のネットワークをロードするまでの間、そのセルを書き換える必要がないからだ。

もちろん大規模なネットワークを無理やりロードしようとしたら、毎回メモリーセルの内容を書き換える必要があり、これはおそらくメモリーセルの寿命を加速度的に縮めることになる。ただMythicのIPUはそこまで大規模なネットワークを扱う予定はないし、そもそも演算器といってもただのフラッシュメモリーだから、通常のプロセッサーよりもはるかに高い演算密度を実現できる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ