今回のお題は3D V-NAND。結論から言えば「Samsungの商標です」で終わりなのだが、これで終わらせると編集部から石が飛んできそうなので、もう少し細かく紹介する。

V-NAND自体が立体構造なのに

それに3Dが付く謎

そもそも、3D V-NANDという言い方は変である。というのは、V-NANDがVertical NANDの略であり、ここに3Dをさらに付けたものを無理に日本語化すると「3次元立体構造NAND」的な表現になる。

だいたい、3DでないVertical NANDがあるのか? というともちろんそんなものはない。実際Samsung自身は「公式には」“3D”をつけずに、ただのV-NANDとして表現している。

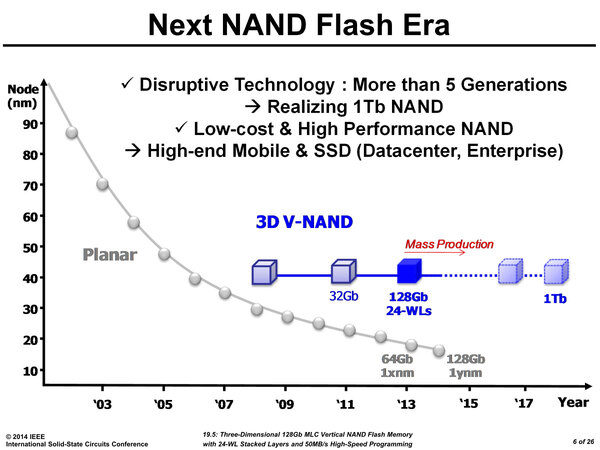

では非公式では? というと、量産型第一世代のV-NANDについて2014年にISSCC(International Solid-State Circuits Conference:国際固体素子回路学会)に同社が論文を発表した際のスライドの一枚がこちら。

画像の出典は、SamsungのISSCC 2014における論文より”

ちなみに論文のタイトルは“A 128Gb 3b/cell V-NAND Flash Memory with 1Gb/s I/O rate”でどこにも3Dが出てこないのだが、発表のスライドで使っていれば、それは言葉が普及しようというものである。

Samsungは2017年のISSCCでは“A 512Gb 3b/cell 64-Stacked WL 3D NAND Flash Memory”というタイトルの論文を発表しているのだが、これがIEEEに収録される時には“A 512Gb 3b/cell 64-stacked WL 3D V-NAND flash memory”に変わっていて、それで特に問題もないあたり、もう3D V-NANDという呼び方をSamsung自身が黙認している状況に近いのではないかと思う。とりあえず本稿では以後V-NANDで通すことにする。

容量を増やすとセルの寿命が縮む

NAND Flashの構造

Samsungが量産している3D NAND FlashがV-NANDというわけで、これはそもそもSamsungの商標であるが、では3D NAND Flashは通常のNAND Flashとなにが違うのだろうか? その話の前準備として、簡単にNAND Flashの構造をおさらいしておく。

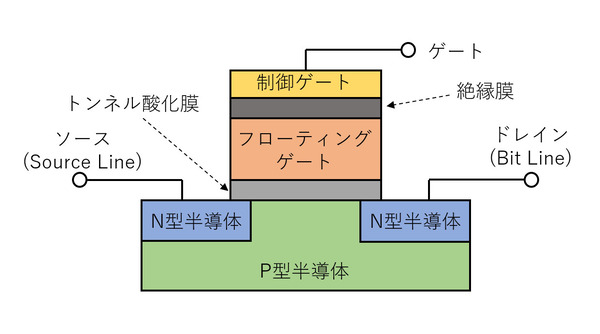

下図が、NAND Flashの構造の模式図(これをセルと呼ぶ)である。この中で、フローティングゲートと呼ばれる部分が、電荷を格納する部分である。要するにこの中に電荷が格納されていれば1、格納されていなければ0となる。

この読み出しは簡単で、電荷が入っているとソースからドレインに電流が流れる。ところが電荷が入っていなければ電流が流れない。したがって、電流が流れるか否かで0と1が簡単に判別できるという仕組みだ。

ちなみに0/1は、いわゆるSLC(Single Level Cell)の方式である。これでは容量があまり稼げないということで、最近はMLC(Multi Level Cell:0/1/2/3)や、TLC(Triple Level Cell:0~7)の製品が主流になっており、さらにベンダーはQLC(Quad Level Cell:0~15)を現在開発中である。

1つのセルに複数の値を保持させようとしているわけだが、原理そのものは簡単でフローティングゲートに格納する電荷の量を2/4/8/16段階に調整する。これに応じてソースからドレインに流れる電流が変化するので、その変化を捉えて値を読み出そうという仕組みだ。

ただ、実はこうした多値化はそのままセルの寿命低減をもたらす。話をSLCに戻すと、読み出しそのものではあまり劣化は生じない。問題は書き込み(0→1)と消去(1→0)である。

フローティングゲートに電荷を蓄えるためには、制御ゲートに高電圧(20V程度)、ドレインに0Vをかければいい。すると、ドレインから電荷がトンネル酸化膜を突き抜けてフローティングゲートに集まる。

逆に消去する場合、制御ゲートに0V、ソースに高電圧をかければいい。すると電荷はフローティングゲートからソース側に流出して空になる。トンネル酸化膜は一種の絶縁体であるが、電荷が絶縁体を飛び越えて移動する現象は、トンネル効果の一種で「ファウラ・ノルドハイム・トンネル」と呼ばれている。

さて、ここでトンネル効果の物理的な側面を長々と説明するつもりはないのだが、何度も電子が酸化膜越しに出入りを繰り返すと、当然酸化膜はボロボロになっていく(格子欠陥と呼ぶ)。この結果として、ある程度ボロボロ度が進むと、ある時に絶縁膜に大穴が開いてしまい、もう酸化膜が絶縁体の役を果たさなくなる。これがセルの寿命である。

この寿命がどのくらいか、というのは製品やプロセスにもよるが、一般にSLC NANDだと数十万回の書き込み寿命があるとする。これがMLCだと1桁減って数万回、TLCだと数百~数千回、QLCは数十~数百回などと言われているのは、書き込み方に問題があるためだ。

例えばSLC NANDでは0か1だが、MLC NANDでは0~3(実際は0/0.25/0.5/0.75)ということになる。これを一発で書き込むのは難しいので、例えば0.75ならまず0.5を1回書き込み、ついで0.25を継ぎ足しするという2回の書き込みになる。

TLCなら0.5/0.25/0.125、QLCなら0.5/0.25/0.125/0.0675を連続して書き込むわけで、その分急速に酸化膜が劣化し、結果として短い寿命につながっていく。

余談だが、この複数回の書き込みが必要、という特性はそのまま書き込み時間の増加=書き込み速度の低下につながる。また読み込みについても、2値ならそれなりに高速だが、4/8/16値ともなると、そもそも読み出しの値の差が少ないので、後処理(主にエラー訂正周り)でいろいろ細工をしてやらないといけないこともあり、その分やや遅くなる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 - この連載の一覧へ