ロードマップでわかる!当世プロセッサー事情 第581回

謎が多いGeForce RTX 3000シリーズのプロセスとGDDR6X NVIDIA GPUロードマップ

2020年09月21日 12時00分更新

AIプロセッサー連載は来週から再開予定だ。というわけで今週はNVIDIAの話をお届けしたい。言うまでもなくGeForce RTX 3000シリーズの話である。といっても、GeForce RTX 3000シリーズの話は発表会、アーキテクチャー解説、開封の儀、ファーストレビュー、ゲームレビューとKTUこと加藤勝明氏ががっつりレビューしているので、これを繰り返すつもりはない(というか、勉強になります)。

ではなんの話かというと、プロセス、それと加藤氏にネタ振りされていたGDDR6Xについてだ。

8LPPプロセスがベースとなる

Samsung 8Nプロセス

まずはプロセス。今回NVIDIAがAmpereで採用したのはSamsungの8Nプロセスである。もちろんこんなプロセス、Samsungは標準では提供していない。Samsungのプロセスは連載418回が最後なので、アップデートも兼ねておさらいしよう。

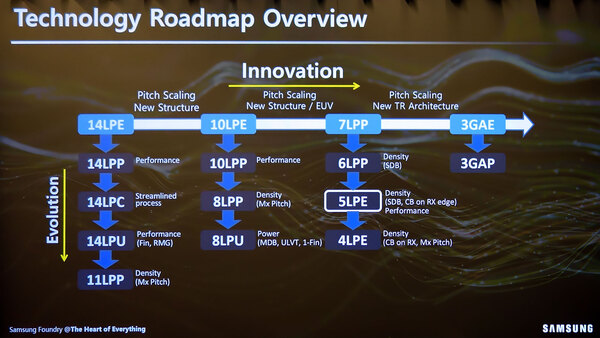

下の画像は昨年10月におけるSamsungのプロセスロードマップである。実際にはこのスライドにあるFinFET/GAA系とは別にFD-SOI系もあり、こちらが最近は引き合いが多いのだが、これは無線通信やIoT向けなど、やや用途がPC系とは異なるのでここではおいておく。

これは2019年10月のArm TechConにおけるSamsungの発表スライドより。毎年細かくロードマップが変わるので、なかなか追いつかない。ちなみに8LPUはむしろ省電力に特化させたものなので、8Nとは違うものだろう

大きなノードとしては14LPE、10LPE、7LPP、それと3GAEの4世代がある。

| 各ノードの違い | ||||||

|---|---|---|---|---|---|---|

| 14LPE | FinFETプロセスの第1世代。この14LPEと、これを改良した14LPPはGlobalfoundriesにもライセンスされた。 | |||||

| 10LPE | FinFETプロセスの第2世代。Gate Pitch/Metal Pitchを詰めたことで、より高密度実装が可能になっている。ちなみにこのノードまでがArF(フッ化アルゴン)液浸のマルチパターニングで露光している。 | |||||

| 7LPP | FinFETプロセスの第3世代。さらにピッチを詰める構造になっており、省電力性と高速性を両立できたとしている。このノードから露光にはEUV(極端紫外線)を利用する。 | |||||

| 3GAE | GAA(Gate All Around)構造の第1世代 | |||||

今回の8Nであるが、おそらくベースになっているのは8LPPプロセスである。もともとは10LPEで、これのトランジスタ駆動性能を引き上げた高速版が10LPP。その10LPPのピッチを縮小した(Fin Pitchは変わらず)のが8LPPとされる。Samsungの主要ノードのパラメーターは以下のようになっている。

| Samsungの主要ノードのパラメーター | ||||||

|---|---|---|---|---|---|---|

| プロセス | 14nm | 10nm | 8nm | 7nm | ||

| Fin Pitch | 54nm | 42nm | 42nm | 27nm | ||

| Gate Pitch | 78nm | 68nm | 64nm | 54nm | ||

| Metal Pitch | 64nm | 48nm | 44nm | 36nm | ||

トランジスタの密度という意味では14nm世代(おそらく14LPP)と8nm世代(おそらく8LPP)は14LPPを8LPPに移行すると53%ほど向上する(Gate Pitch×Metal Pitchの比率)計算になるが、Fin Pitchそのものは10nmと8nmで変わらないので、ここまで小さくなるかというと、もう少し低めで45~46%くらいに落ち着くだろう。

ただ、10nm→8nmでは16%程の密度向上でしかなく、実質トランジスタの数は1割程度しか増えない。その意味では、8nmといっても限りなく10nmに近いレベルと言って良い。これは、EUVを使う7nmでは10nmと比べて67%もトランジスタ密度が上がるのと好対照である。

7nmはさらにFin Pitchも大幅に切り詰めているので、間違いなくこれに近いところまでトランジスタ数が増えるだろう。

以上のことから、もし可能であればNVIDIAは7LPPを使いたかったのだろう。この7LPPに関わる話は以前連載563回で説明した通りだ。

A100はおそらくSamsungの7LPPとTSMCのN7の両方で試作を行ない、結果としてSamsungが落ちたと想像するが、ではGeForce RTX 3090に使われるGA102の場合はどうだろう?

GA102は280億トランジスタを、628mm2のダイに押し込めている。もしこれをSamsungの7LPPで製造したら、トランジスタ密度は45%ほど引き上げられる計算になるが、このスケーリング通りに行かない部分もあるから、良くて35%くらいといったところで、ダイサイズは410mm2近辺か。

A100が540億トランジスタでダイサイズが826mm2なので、この比率でいけば280億トランジスタでは428mm2ほどのダイになる計算だが、Samsungの7LPPはTSMCのN7より密度が高いので、410mm2近辺という推定はそう外れていないと思う。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ