ロードマップでわかる!当世プロセッサー事情 第581回

謎が多いGeForce RTX 3000シリーズのプロセスとGDDR6X NVIDIA GPUロードマップ

2020年09月21日 12時00分更新

ビデオメモリーに採用された

Micronの独自規格GDDR6X

GeForce RTX 3000シリーズの発表にあわせ、Micronも正式にGDDR6X SGRAMを発表した。Micronによれば、そもそもデータバスにPAM-4(Pulse Amplitude Modulation-4)を用いるという話は、2006年から手掛けてたという。

もっともこれは製品というよりも研究開発のレベルの話である。実際の製品化に向けた開発のスタートは、2017年だったそうだ。

製品化に向けた開発は2017年にスタートしたと、Micronの“Feeding the Beast: the Making of GDDR6X”でTim Hollis氏(Fellow and Signaling Expert)が発言した

さてまず基本的な話。これまでPCに使われる主要な信号伝達方式はNRZ(Non Return to Zero)という方式で、信号が0か1かのどちらかしかない、というものだ。

“Non Return to Zero”の意味は「『信号がない』という状態がない」の意味である。信号レベルが0だったら、それはデータが0であると見なされ、信号がないとは見なされない。ところがこの方式では、1回の転送で1bit分のデータしか転送できない。

そこで、信号レベルを0と1でなく、-3/-1/1/3と4値にすれば、1回の転送で2bit分が転送できる。これがPAM-4である。実際にはもっと多いPAM-8(信号レベルが8段階、1回の転送で3bit送れる)やPAM-16(信号レベルが16段階、1回の転送で4bit送れる)なども実用化されている。

この仕組み、最近のNANDフラッシュを考えてもらうとわかりやすい。NRZというのはSLC NAND、PAM-4がMLC NAND、PAM-8がTLC NANDというわけだ。

実はネットワークの世界では、このPAMは次第に広く利用されるようになってきた。100Gbpsを超えるイーサネットでは、PAM-4を併用して1レーンあたり50Gbpsや100Gbpsを実現するのが普通になってきた。

あるいは現在使用策定中のPCI Express Gen6も、信号速度そのものはGen5と同じ32GT/秒であるが、PAM-4を併用することでレーンあたり64Gbpsを達成する見込みである。技術そのものはかなり昔からあったもので、それほど珍しい話ではない。

さてそのMicronであるが、もともとGDDR5とGDDR6の間にGDDR5Xを挟む形で、独自規格のメモリーを出すことにそれほど抵抗はなかった。

GDDR5Xの場合、後追いでJEDECの標準化も行なわれたが、結局これを採用したのはNVIDIAのGeForce GTX 1000シリーズのみだったこともあってか、MicronによればGDDR6XをJEDECで標準化するプランは今のところないとされる。

さてそのGDDR6Xであるが、これはGDDR7の策定が遅れており、その一方でGDDR6はピンあたりが16Gbpsが限界となっているため、これ以上の帯域を得ようとすると以下の対策が必要となる。

| 帯域を得るための手段と課題 | ||||||

|---|---|---|---|---|---|---|

| 手段 | 課題 | |||||

| HBM2/2Eに移行 | Silicon Interposerが必須となる関係で、チップそのもののコストが上がるうえ、HBM2/2Eのコストも高い。またチップ製造の後工程の段階でメモリーチップの容量が決まってしまうので、OEMがメモリーの容量を変更できない(NVIDIA側で2種類のメモリー容量を持つチップを準備する必要がある)。 | |||||

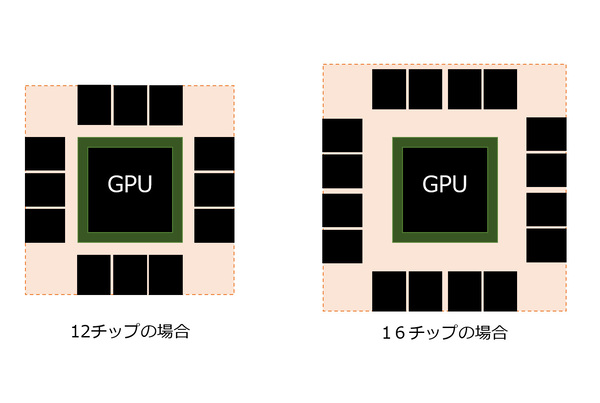

| チップの数を増やす | 今ですら384bit(=12個)のチップを無理やりGPUの周りに苦労して配している状況であり、これを増やすとなると配線距離を伸ばしてGPUから少し遠いところにメモリーチップを置く形になる。 そうでなくても信号が高速化しており、なるべくGPUのそばにメモリーチップを置きたいという最中にむしろ距離を伸ばして離れたところにメモリーチップを置くというのは許容しがたいし、ボードの大型化にもなる(メモリーチップが離れているということは、VRMはさらに離れたところに置かれるわけで、この配線損失にともなう発熱も問題になる)ので、許容しがたい。 | |||||

したがって、HMB2/2Eと多チップ化のどっちもどっち、という状況に対する解が、PAM-4を使うことで帯域を引き上げて解決する、というGDDR6Xだったわけだ。

さて、GDDR6XでPAM-4を使うことのメリットは他にもある。1回の転送で2bit送れるということは、転送速度自体は半分に減らせるという意味でもある。

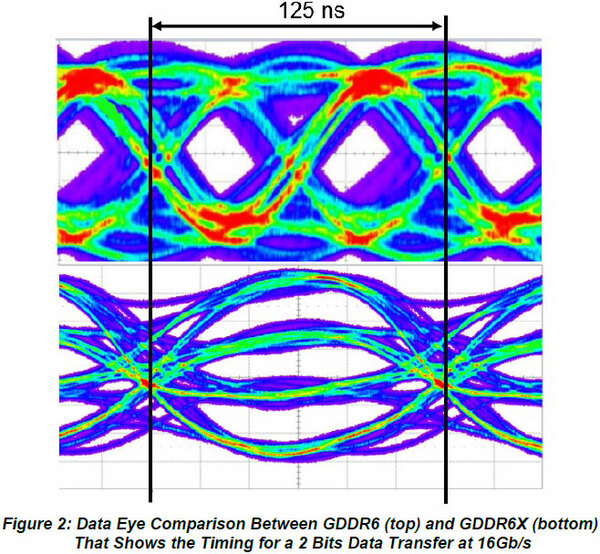

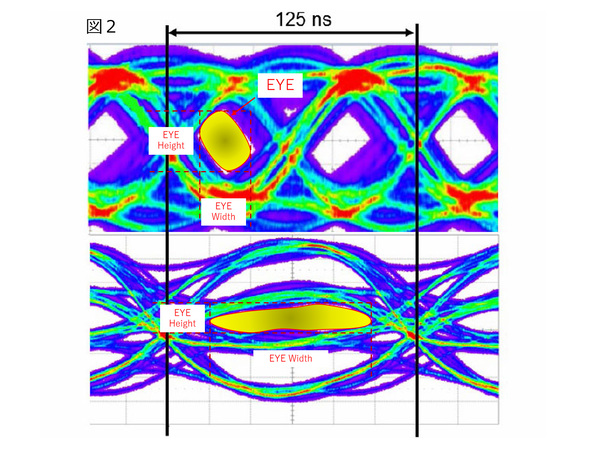

下の画像はMicronが提示する、16GbpsをNRZとPAM-4で送った場合の波形を比較したものだ。ここで信号の合間をEYEと呼ぶのだが、そのEYEの高さ(EYE Height)と幅(EYE Width)が信号伝達では重要になる。

下図でNRZ(上)とPAM-4(下)を比較すると、EYE Heightそのものは確かに半分ほどに下がる。その一方でEYE Widthそのものは2倍に広がることになり、より長時間のSampling & Holdが可能になる。

また信号のバラつきそのものもPAM-4の方が少ない。これは信号の周波数そのものが半減していることに起因するため、実はPAM-4でもそんなに信号伝達は難しくないことが見て取れる。

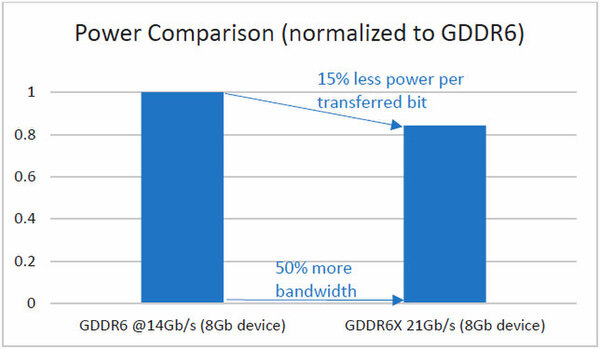

さらに言えば、信号速度が落とせる分、信号伝達に必要な電力が減るというメリットがある。実際Micronによれば、14GbpsのNRZと21GbpsのPAM-4で1bitを転送するのに必要な電力は、PAM-4の方が15%少ないとしている。

1bitを転送するのに必要な電力は、PAM-4の方が少ない。もっともこれは1bitあたりの電力なので、2bit分を転送する実際の消費電力という意味では21Gbps PAM-4は14Gbps NRZの70%増し、ということでもある

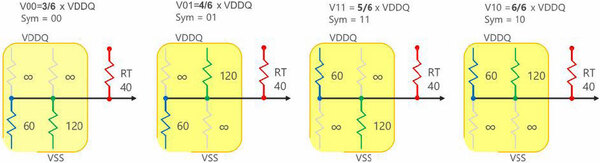

ところでこのPAM-4のエンコードやデコードのために、メモリーチップに複雑な回路を入れるのはコスト的に難しい。このためGDDR6XのPAM-4のエンコードは下の画像のようなシンプルな方法で実装されている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ