ロードマップでわかる!当世プロセッサー事情 第578回

Ice Lake-SPはスループットがSkylake-SPの2倍以上になる インテル CPUロードマップ

2020年08月31日 12時00分更新

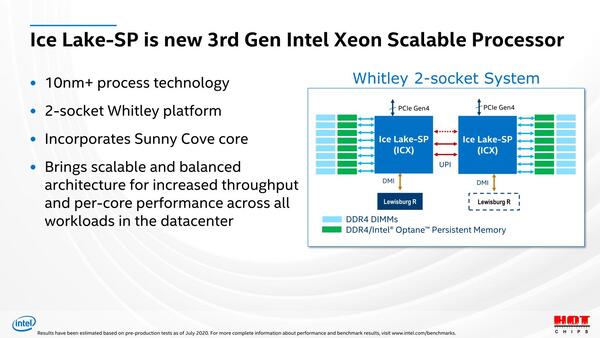

前回のTiger Lakeに続き、Ice Lake-SPの話題をお伝えしよう。Architecture Dayでは下の画像がIce Lake-SPに言及した唯一のものだったので、話はHot Chips 32で公開された情報が主なものとなる。

Ice Lake SPはIce Lakeと同じ10nmプロセス

PCIe Gen4に対応するがDMIの接続はPCIe Gen3のまま

さて、まずは基本的なところから。Ice Lake SPはSunny Coveコアをベースとし、プロセスは10nm+、つまり10nm SuperFinではなく、現行のIce Lakeと同じ10nmプロセスで製造される。

Ice Lake SPはIce Lakeと同じ10nmプロセス。UPIは原則2 Pairでの接続。3つ目が破線というのは、その気になれば3 Pairでの接続も可能という意味だろうか? もっとも、原則3 Pairながら、UPIを他のデバイス(Agilex FPGA)を接続する場合は2 Pairでの動作も可能という意味かもしれない

チップセットはLewisburg Rとされる。Lewisburgは現在のXeon向けのC620シリーズチップセットであるが、この世代はDMIがPCIe Gen3×4の構成である。

一方Ice Lake-SPはPCIe Gen4に対応しているが、後述するようにDMIの接続は引き続きPCIe Gen3になっており、チップセット側のPCIe Gen4対応は次のSapphire Rapids世代までお預けになるようだ。つまり、Lewisburg Rは、単にIce Lake-SPでも動くようにしたC620シリーズそのままと思われる。

したがって、Ice Lake-SP対応のマザーボードでPCIe Gen4が利用できるのはCPUから出るPCIeレーンに限られ、チップセットから出るものは引き続きPCIe Gen3のままになる。

もっともチップセットに接続するデバイスはオンボードの10Gイーサネットコントローラーやブート用のM.2 SSDなどに限られ、アクセラレーターなどPCIe Gen4を必要とするものはx16スロット経由になるためこれで問題はないのだろう。

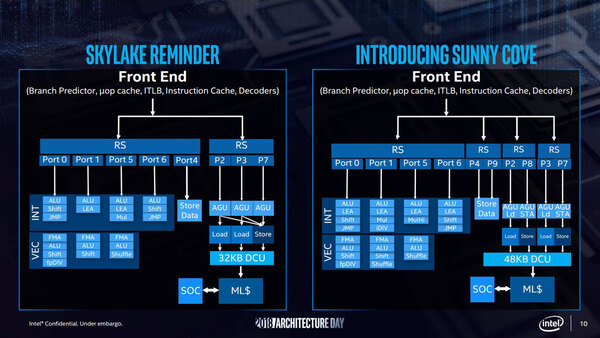

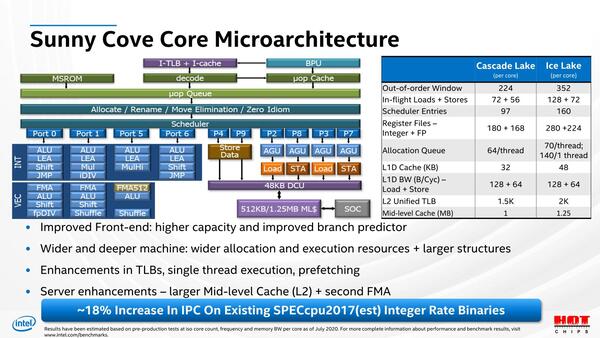

なおIce Lake-SPのWhitleyプラットフォームは1/2 Socketに限られるという話は、連載569回にも出てきた話だ。そのSunny Coveコアについてだが、基本的な構造そのものは2018年に発表されたものそのままである。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ