消費電力を最大75%削減

Renoirは単にZen 2+Vegaで周辺回路を強化した程度か? というともちろんそんなことはない。最大の特徴は省電力機構にある。

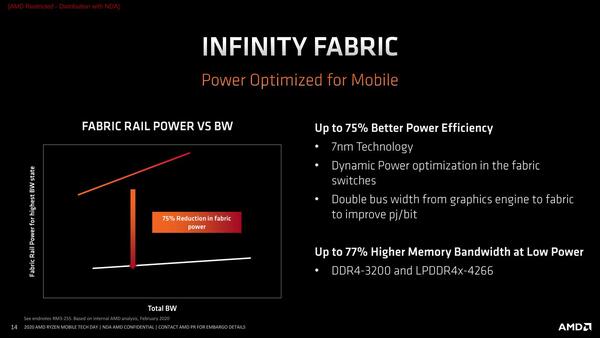

まずインフィニティー・ファブリックそのものは同じZen 2といっても、Matisseの場合はCPUチップレットとI/Oチップレットが別々のダイになっており、それなりに高い電圧で信号を送らないと減衰してしまい、これが理由で消費電力がやや大きいという欠点があった。

ところがRenoirの場合は1チップのモノリシック構造なので、そもそもチップ外部にインフィニティー・ファブリックを引き回す必要がない。このため、バス幅を倍増させ、その一方でおそらく伝達速度そのものを半減させたことで、消費電力を最大75%削減できたとする。

チップ内部だけで良ければ引き回し距離も大幅に減り、電圧も大幅に下げられるわけで、このあたりも効果的だったと思われる。

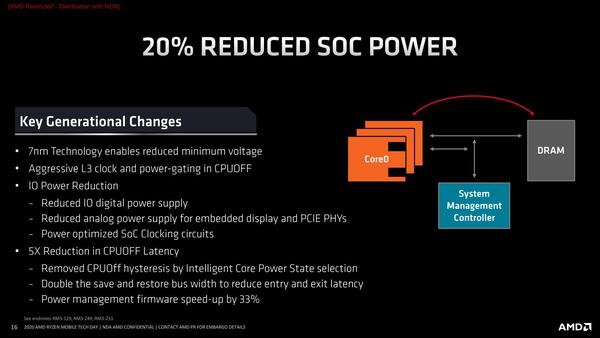

一方、下の画像はRaven Ridge/Picassoとの比較と思われるのだが、SoC周りの消費電力を大幅に削減できたとする。正確に言えば「SoCに統合されるCPUの電力管理メカニズム」で、インフィニティー・ファブリックのうちコントロール・ファブリックを利用して制御されている部分だ。

このCPUの電力管理に関して言えば、ACPI 6.3への対応も新しく追加された。

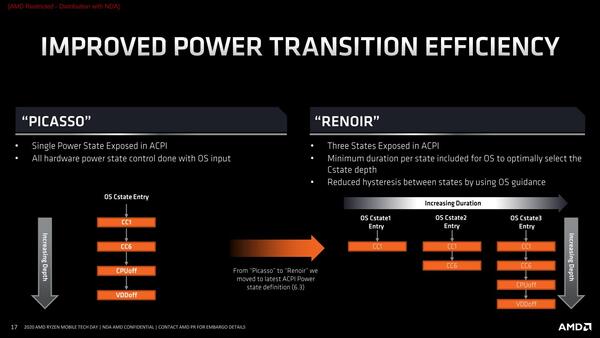

通常待機状態になると、CC1(稼働中)→CC6(スリープ)→CPU Off/Vdd Off(シャットダウン)という具合にだんだん深い省電力モードに入るのだが、CC6はともかくCPU Off/Vdd Offまでいくと、そこからの復帰には結構な時間がかかる。そこでACPI 6.3では新たにLPI(Low Power Idle)ステートという値を追加した。

例えばLPI1ならCC1より下には落ちず、LPI2ではCC6どまり、LP3だとVdd Offまで落ちるといった設定をしておけば、あとはOSが動作状況に応じてどのLPIステートにするかを選択できるというものだ。

省電力性だけを考えれば常にVdd offまで落ちるのが一番省電力に見えるが、これが煩雑に繰り返されるようならCC6止まりにしておいた方が結果的に省電力という可能性もある。

もっともこれにはOS側の対応も必要なのは当然で、現状Windows 10でこれがサポートされているかどうかは今回未確認である。別のスライドでは、WindowsのPower slider UIで調整できるかのように書いてはあるのだが、明示的にLPIを制御しているとは明言していないので、確証がない。

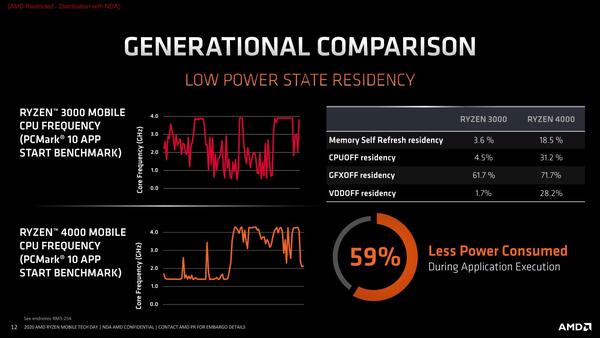

実際にPicasso世代との省電力比較をした結果が下の画像だ。PCMark 10のApp Startup Benchmark実施中の動作周波数の変動とCPUのステートを見たものだが、CPU待機時間もRenoirの方がずっと多いし、CPU/GPU Offのみならず、Vdd Offの時間も圧倒的にReniorの方が長い。結果として、59%もの節電が可能になったとしている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ