X570チップセットに

第2世代Ryzenを載せたときの挙動

次にチップセット周りについて。連載513回の最後で、X570に第2世代Ryzenを装着した場合にどういう振る舞いになるのか、という点が不明だとしたのだが、これについて確認が取れた。

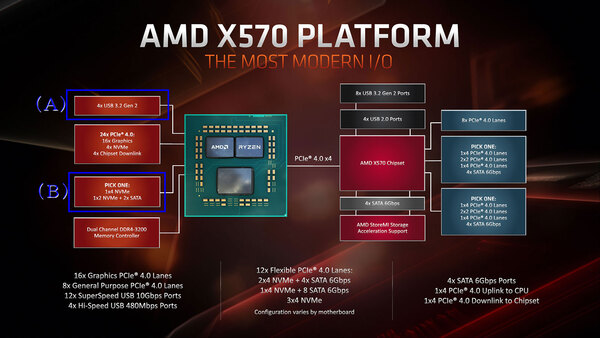

まず上の画像の(A)にあたるUSB 3.2 Gen2×4であるが、これは第2世代Ryzenを搭載した場合、USB 3.1 Gen1相当(USB 3.2 Gen1といっても良いが、要するにUSB 5Gbps相当)にダウンするとのこと。

次いで(B)の、1×4 NVMeに関しては第2世代Ryzenでは無効になるという話であった。おそらくではあるが、第2世代RyzenのCPUピンにはそもそもこの1×4 NVMe向けのPCIeの信号が出ていないのではないかと思われる。

またGPU接続用のx16のPCIeレーンも、X570との接続用のx4 PCIeレーンも当然Gen3相当になり、この場合X570から出るPCIeもすべてGen3相当になるという話だった。

ただこの場合でも、チップセットから出る8ポートのUSB 3.2 Gen2ポートはそのままUSB 3.2 Gen2として有効とのことであった。これは妥当な構成なのではないかと思われる。

メモリーはDDR4-5133まで可能

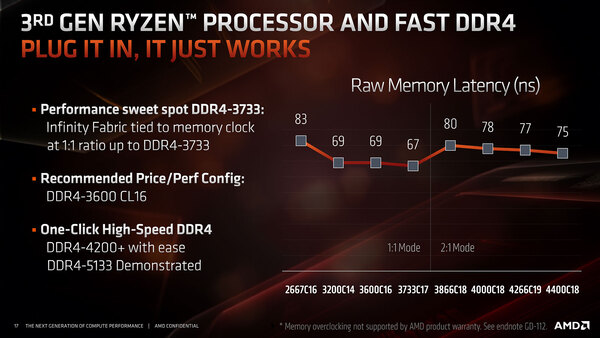

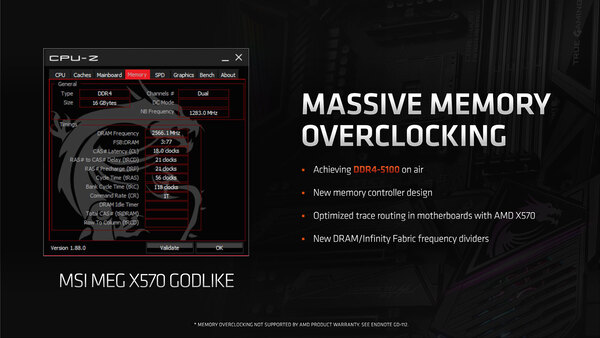

チップセットの話が出たところでついでにメモリーコントローラーの話もしておこう。第3世代Ryzenは、定格がDDR4-3200まで、という話は連載513回でレポートしたが、実際はというとDDR4-4200あたりまでは軽く行けて、DDR4-5133までは可能という説明があった。

ここに出てくる1:1Modeと2:1Modeであるが、これはメモリークロックとインフィニティーファブリックのクロック比である。

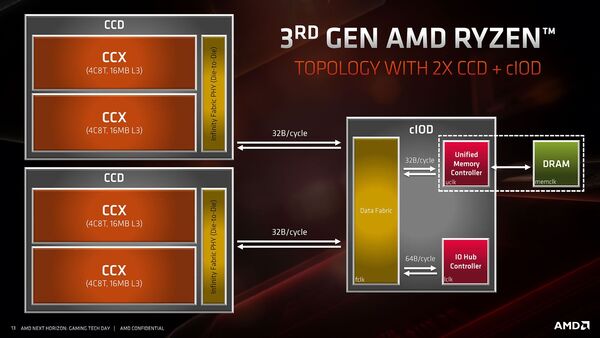

前回の記事の図で、I/Oチップレット(cIOD)側を見ると、メモリーのクロック(memclk)とメモリーコントローラーのクロック(uclk)、それとデータファブリックのクロック(fclk)が別々のクロックソースになっていることが示されている。

1:1 Modeの場合、memclkとuclkが連動し、ということはuclkとfclkも連動するために、あまりmemclkを上げすぎるとインフィニティーファブリックのスピードが上がりすぎて動作しなくなる。

そこでDDR4-3866(つまりmemclkが1933MHz)以上の場合、uclkとfclkの比を2:1にすることで、インフィニティーファブリックの速度が上がりすぎないようにできるという話である。これを利用すれば、DDR4-5133も夢ではないというわけだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ