順次後継機をリリース

プロセッサーのダイサイズが大型化

このあと2002年にはやや性能と価格を落としたeServer z Series 800を9製品発表するが、これはプロセッサーそのものはz900そのままである。これに続き2003年5月に投入されたeServer z Series 990は、プロセッサーもz990に切り替わる。

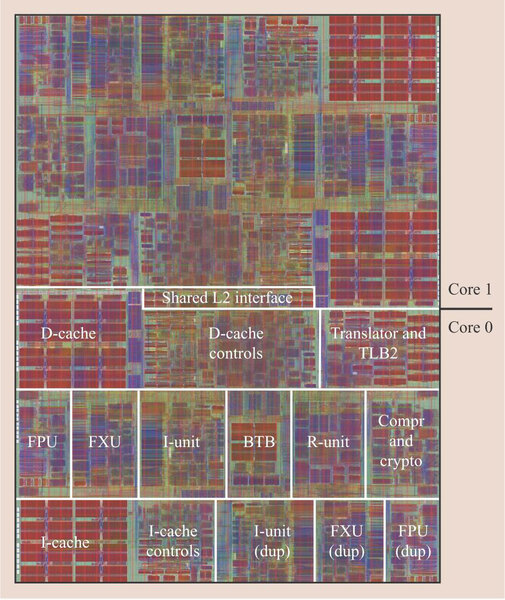

こちらはパイプライン段数こそ同じものの、2命令のスーパースカラーを搭載(ただしIn-Order)、プロセスもCMOS 9S(0.13μm SOI)となり、動作周波数は1.2GHzに引き上げられた。ダイは2コア構成となっており、ダイサイズは19×14mmで、2コアの合計で消費電力は55Wと発表されている。

画像の出典は、IBM Journal of Research and Development Volume 48, Issue 3.4, May 2004

ダイサイズが大きくなった分、MCMは1個あたり8ダイ(16コア)構成になっており、ハイエンド品はMCMを2つ搭載した32way構成になった。

このz990 CPUを利用した低価格帯向けモデルが2004年に発表されたeServer z Series 890となる。2005年には名称がeServer z SeriesからSystem zに変更され、その最初の製品がSystem z9となった。

プロセッサーはz9 CPUであるが、これはz990 CPUを90nm SOIプロセス(CMOS10S)化したほか、特に周辺回路を大幅に再設計し直した構造である。プロセッサーのダイはデュアルコアで、1つのMCMに8ダイ(16コア)が搭載されるという構造はz990 CPUと同じである。

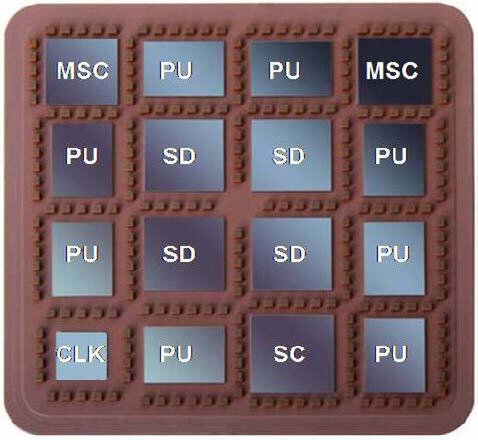

画像の出典は、Mainframe hardware course: Mainframe's processors

ダイサイズは11.844×15.778mmとやや小型化し、動作周波数は1.7GHzに引き上げられた。ただプロセッサーの内部構造そのものにはほとんど手が入っていない(命令の追加などは行なわれているが、大きな構造の変化はない)ため、性能向上はほぼ動作周波数の向上によるものである。

一方、周辺回路であるが、SC(Storage Controller)経由で4つのSD(System Data)がぶら下がる構造は似ている(ただし容量はSD1個あたり40MBに達している)が、これとは別にMSC(Memory Storage Controller)というチップが2つ追加され、MCMの外部に3次キャッシュを接続できるようになっている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ