2次元パターンの配線を作れない

SAQP(Self-Aligned Quadruple patterning)

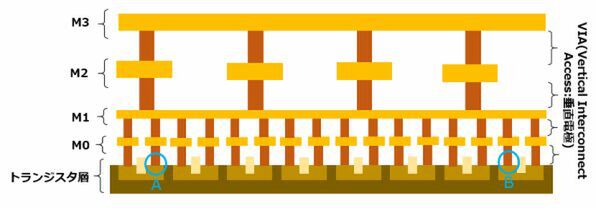

配線をやり直すというのはどういうことか。下図は簡単な模式図だが、例えば左端にあるFinFETのドレイン(A)を、右端のFinFETのソース(B)につなぎたいと思ったとする。

従来なら、可能であればM0/M1を使って接続する形になっていたわけだ。

これを、より抵抗の少ないM2以上を使って接続するようにして、M0/M1の利用頻度を減らそうということだ。この技法はVIA Pillarと呼ばれている。

これは、言うは簡単だが実際にやるのはかなり困難である。まず、そもそもM2以上の配線層が遊んでいるならば簡単だが、実際にはそんなことはなくギッチギチに詰まっているわけで、これを無理やりどけてM0/M1を使っていた配線層をM2以上に持ち上げるのは、かなりの難易度である。

場合によってはM10までで済まず、M11やM12まで必要になるかもしれない。この時点でまず既存の配線層がそのまま使えないことになる。

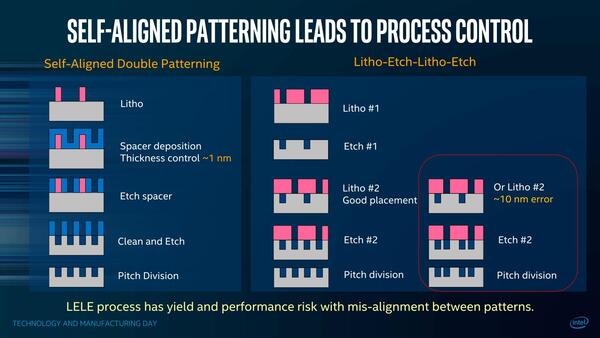

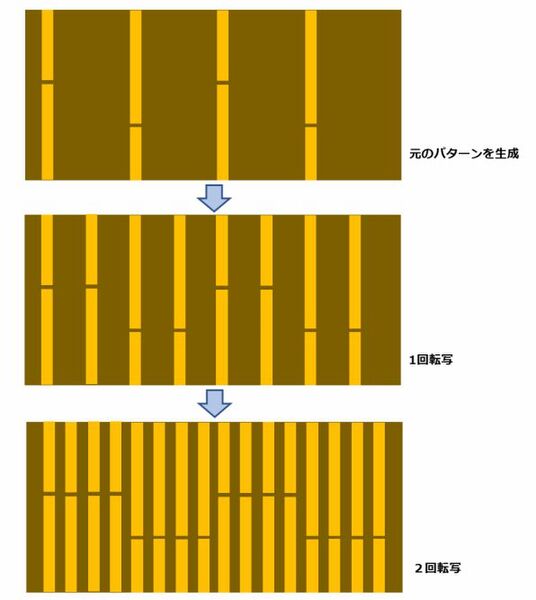

これに輪をかけて難しくしているのがSAQPである。これもちょうどインテルのスライドに説明があったので使わせていただくと、配線層(トランジスタ層でもそうだが)を構築する場合、SADPとLELEという2種類の方式がある。

SADPは下の画像の左側で、まずマスクから露光してパターンを作った後で、そこに薄膜(厚さ1nm程度)を構築、ついで余分な部分を抜くことで、もともとのパターンの半分の間隔でパターンを作れる。

SAQPはこれを2回繰り返すことで、元のパターンの1/4の間隔でのパターン構築ができる。対してLELEは露光→エッチングをした後で、その上に別のパターンを再び露光→エッチングすることで、細かいパターンを作りこむというものだ。いわゆるダブルパターニングといえば、普通はLELEを指すことが多い。

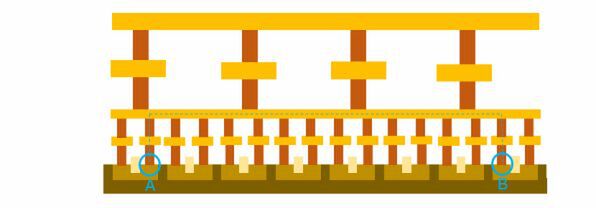

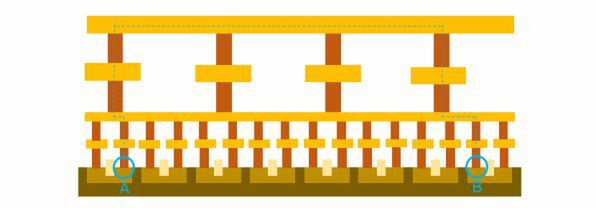

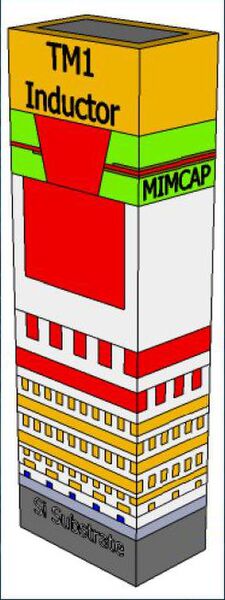

問題は、SADPでもSAQPでもそうだが、2次元パターンは作れないことだ。下図は冒頭のスライドの左側の立体を抜き出したものだ。気を付けて見直してほしいのだが、黄色や赤の配線は、よく見ると1次元配線になっていることがわかる。

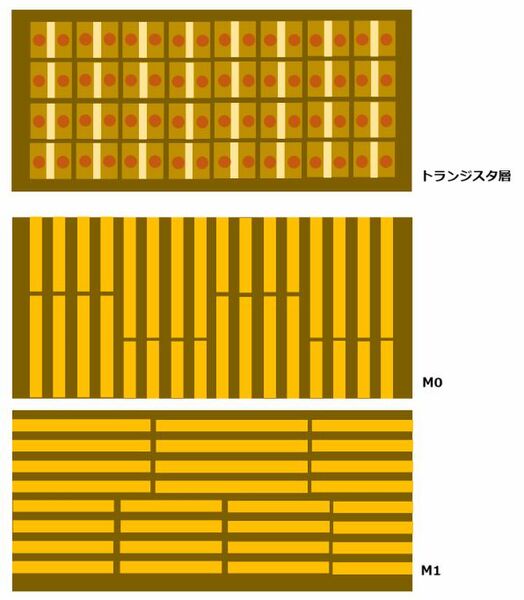

先の模式図を上から見た場合のトランジスタ層とM0/M1層は、下図のような格好になっている。あとは必要なところにVIAを打って回路をつなげるという形だ。

さてこの図でM0/M1の配線が4本一組なのは、もちろん意味があってのことである。SADPなら2組、SAQPなら4組単位でしか配線を行なえない、というのがSADP/SAQPの大きな欠点である。当たり前の話で、SAQPは下図のように構築するので、4つ一組にしかなりえない。

また図で言えば、横方向に伸びるパターンは、転写したパターンとくっついてしまうため原理的に作れない。もちろん端から端まで貫通するようなパターンならば生成できるが、M0/M1でそうしたパターンは普通使われない。

こうなると、M0/M1経由でM2以上に配線を逃がす作業そのものが強烈に難しくなる。あるトランジスタの配線を迂回しようとすると、そこから始まる4つ分のトランジスタの配線を全部同じように迂回させなければいけないわけで、設計が極めて困難なのは火を見るより明らかである。

ちなみにLELEなら2次元パターンも構築できるのだが、実はLELE程度ではコストの増加は無視してもピッチ36nmの配線は非常に難しい。最低でもLELELE(露光→エッチングを3回繰り返す)になるが、今度はちょっとしたマスクのずれが致命的な結果になりがちで、実際量産過程で適用するのはかなり困難である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第876回

PC

このままではメモリーが燃える! HBM4/5世代に向けた電力供給の限界と、Samsungが示すパッケージ協調設計の解 -

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 - この連載の一覧へ