Turbo機能の実装で

TDPと消費電力に乖離が生じる

K6やPentium Proの世代までは、おおむね「消費電力≒TDP」の図式が成立したし、この後もしばらくはあまり大きな違いがないまま推移した。

このあたりがずれ始めるのは、インテルはPentium 4、AMDはFXの時代からである。どちらもIPC(Instruction per Clock)はそこそこで、動作周波数を思いっきり引き上げる方向のプロセッサーだ。必然的に消費電力も増えることになったのだが、逆にこれらのプロセッサーは負荷がかかっている時とかかっていない時で、消費電力の差が非常に大きいという特徴を持つ。

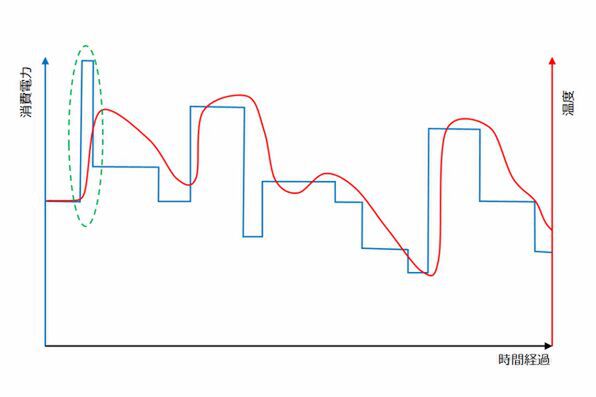

この結果、下図のように温度と消費電力の間に明確なずれが生じ始めるようになった。 消費電力が急に上がっても、温度が上昇するまでに若干(数ミリ秒だが)のずれが生じるようになったわけだ。つまり、温度は95W相当であっても、消費電力そのものは110Wくらいあるというケースがしばしば出るようになってきた。

この傾向はその後インテルやAMDが、一時的に動作周波数を引き上げるTurbo機能を実装することで、さらに顕著になった。

図で言えば、緑の破線で囲んだあたりがこれに近い。非常に短い時間だけ動作周波数を引き上げることで、消費電力もこれに応じて急激に増えるが、発熱が増えるのはワンテンポ遅れてからとなる。その際に、急速に消費電力が下がれば、つまりTurbo動作が一瞬で終われば、発熱はそれほど増えないことになる。

このあたりになって、いわゆる消費電力とTDPは大きく乖離することになった。もちろん、動作周波数をいっさい変えずにひたすらフル回転させる状態、たとえば全コアを使ってのレンダリングやエンコード、オンプレミスの企業内サーバーの類、あるいは長時間を要する科学技術計算などの場合には、消費電力とTDPがほぼ一致する。

また、そもそもTDPが低い環境、インテルで言えばCore m製品などがこれに該当するが、この場合も動作周波数を変化させるといっても、そもそも熱的なマージンが非常に小さいので、消費電力とTDPの乖離がそれほど大きくできない。それもあって、やはりTDPと消費電力の差はそう大きくない。

問題は特にデスクトップPCなどで、TDPと消費電力の乖離は非常に大きなものになっている。たとえば先のCore i7-8700Kの場合。定格(Processor Base Frequency)は3.7GHzとなっており、Max Turbo Frequencyが1GHzアップの4.7GHzである。

TDPは95Wだが、このTDPの定義はインテルによれば“Thermal Design Power (TDP) represents the average power, in watts, the processor dissipates when operating at Base Frequency with all cores active under an Intel-defined, high-complexity workload.”となっている。

ラフに訳せば「TDPとは平均的な消費電力、つまりBase Frequencyですべてのコアが稼動している状態で、インテルが定義する複雑なワークロードを実行した場合にプロセッサーが消費する電力をWで表現している」というあたり。

要するに3.7GHzで全コアが動いている状態での消費電力に相当するものがTDPであり、Turboがかかった状態では一時的にこれを超える場合が当然ありうる。この結果として、設計者に対してはTDPとは別に、電源設計のガイドラインが示されており、こちらで最大消費電力が推察できるようになっている。

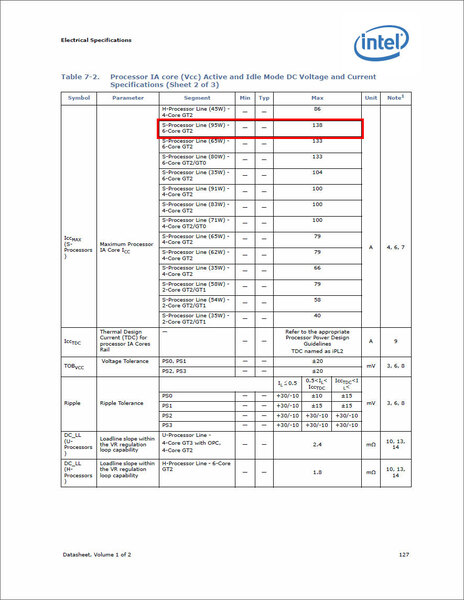

Core i7-8700Kの場合、データシートによればプロセッサーに対して最大138Aを流せるようにしておく必要があるとされる。

画像の出典は、“8th Gen Intel Core Processor Families Datasheet 1 of 2”

では、電流は最大138Aだとして電圧は? というと、別のところに記載があるのだが、Sシリーズの場合には最大1.54V、典型値だと1.05Vとなっており、1.05×138=144.9Wというおそろしい数字が出てくる。

もちろんこれは一瞬の話であって、常時この消費電力になることはありえない。MAXはあくまでも仕様上の最大値であって、実際にはここまで行くことはまずないのだが、95Wより多くなるのは日常茶飯事であり、マザーボード設計者は最大145Wに備える必要があるわけだ。

このあたりの事情はAMDも同じである。AMDはRyzenからXFR(Extended Frequency Range)という、さらに動作周波数を引き上げる仕組みが入ったので、より乖離が大きくなったというべきだろう。

ただ、発熱が多くなって熱的なマージンが減ってくると、動作周波数をそうそうあげられなくなるので、長期的に見れば消費電力とTDPは近づいてくる。その意味では、「消費電力≒TDP」の図式はそう外れてはいないのだが、現実的には「消費電力≒TDP+α」くらいに考えておくのが無難であろう。

※お詫びと訂正:記事初出時、消費電力と温度に関する記述で、誤解を招く表現がありました。記事を訂正してお詫びします。(2019年2月28日)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ