微細化すると寿命が縮むため

メモリーを縦に積むことで容量を稼ぐ

セルの寿命の短さを助長しているのが、微細化である。冒頭のスライド画像に戻ると、容量を増やすためにものすごい勢いで微細化を進めているのがわかると思う。

ところで、微細化というのは、セル全体の寸法をそのまま縮めるという意味であり、すると必然的にトンネル酸化膜も薄くなっていく。ということは、その分早く酸化膜が寿命を迎えるという意味であり、これがそのまま寿命の短縮につながることになる。

また微細化そのものも、このところ頭打ち気味であり、容量は増えないわ寿命は縮まるわ、しかしながら大容量化への要望は激しいわ、ということでフラッシュメモリー業界が考えたのは「それでは縦に積みましょう」という策だ。

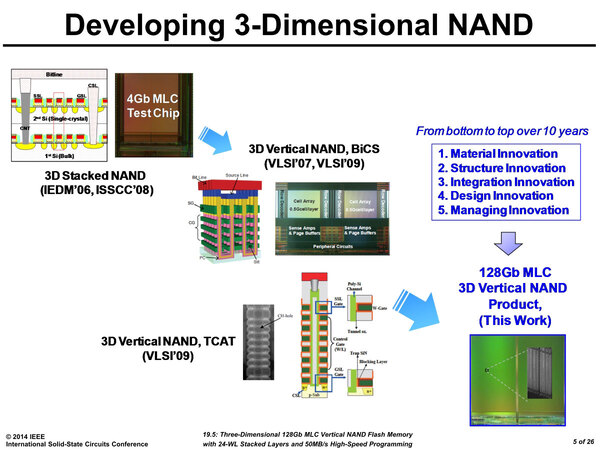

最初は文字通り、素直に複数のフラッシュメモリーを縦積みして、間をTSV(Through Silicon Via:シリコン貫通電極)でつなぐというもの(下の画像の左上)だった。

画像の出典は、SamsungのISSCC 2014における論文より”

これだと確かに容量は稼げるものの、コスト削減にならない(前回も触れたがTSVを構築する分、むしろコストが上がる)ので、根本的な解決にならなかった。

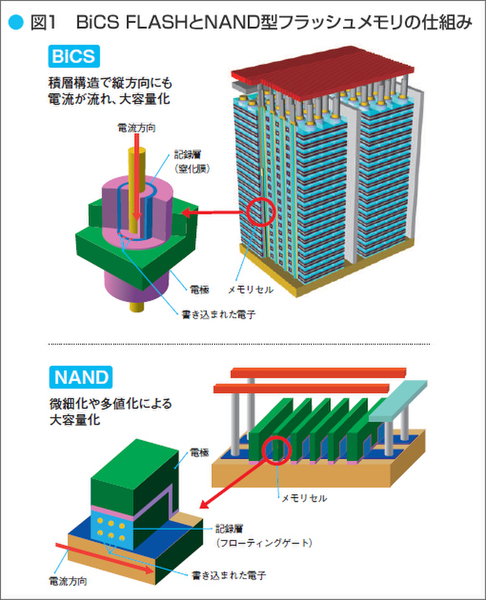

そこで、2次元構造のFlashのセルを縦積みにするのではなく、根本的に3次元構造のセルを開発しましょう、という話になった。これに基づいて2007年に東芝が発表したのがBiCS(Bit Cost Scalable) NANDである。

BiCSの構造の概略は東芝のウェブサイトに掲載されているが、要するに縦方向にセルを並べる構造で、セルそのものも円筒形になっている。

画像の出典は、“東芝科学館”

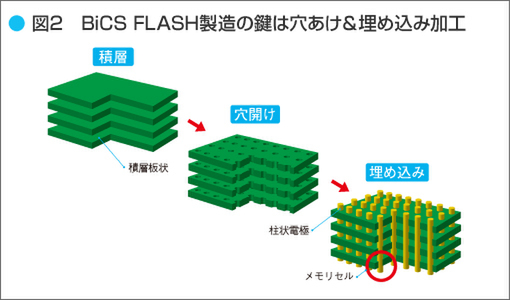

この構造をBit Cost Scalableと呼ぶのは、製造コストが抑えられるからということだ。

画像の出典は、“東芝科学館”

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ