テクニカルセッションとNVIDIAのブログで判明した

Pascalの内部構造

下の画像が全体の構成である。10個のSMをまとめて1つのGPCを構成、これが6つでトータル60個という計算だが、このうち4つのSMは無効化されているので、合計56SMという計算だ。

冒頭のロードマップ図で“GeForce Titan?”のRaster Operationの数が“120?”になっているのは、この無効化と関係ある。上の画像ではRasterizerが省かれているが、普通に考えるとRasterizerはSMとは別の場所に置かれており、SMを無効化してもRastezierは残っているように思われる。

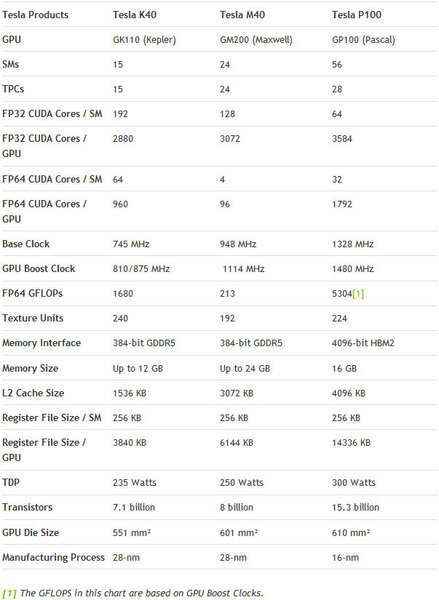

すると、普通に考えれば120基が利用できるはずなのだが、実際にどうなのかははっきりしない。ちなみに3世代のTeslaの特徴をまとめたのが下の画像だ。

倍精度もそうだが、Deep Learningでは単精度ですら多すぎるということで新たにFP16(半精度)がP100ではサポートされており、こちらでのピーク性能は21.2TFLOPSに達しており、MaxwellベースのTesla M40と比べて3倍の性能になる。

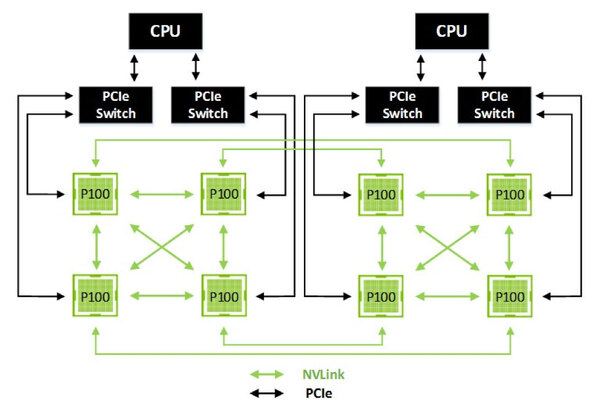

さて、上の画像でも小さく出ているが、GP100では4本のNVLinkが利用できる。NVLinkそのものは4対の双方向リンクになっており、リンク1本あたり40GB/秒、効率94%以上とされる。

効率、というのはおそらくPCI ExpressやUSB 3.0以降と同様にEmbedded Clockを採用しているためだと思われる。94%以上、ということだと64b/66b Encodingあたりを利用してEmbedded Clockを実装していると考えられる。

下の画像がP100×8+Dual CPUの構成で、これはDGX-1の構成向けのものと思われる。

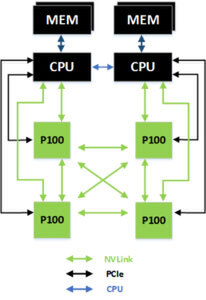

一方P100×4の構成例も示されており、直接NVLinkでの接続も可能とされる。

あとはメモリーの話だが、NVIDIAのブログにはあまり詳細は書かれていない。とはいえHBM2を使うことは明らかにされており、利用されるダイ(HBM2のスタックを構成するメモリーチップ1つ)は8Gbitの容量だとされている。

つまりHBMスタック1つあたり32Gbit=4GB、これを4つ搭載するので16GBという形だ。これをTSMCのCoWoSを使ってGP100コアと接続している。帯域は1チップあたり1024bit/1GHz DDRでの接続なので256GB/秒、4つで1TB/秒という計算になる。

さて、話としてはこの程度だが、ついでにGP104などの構成について少し占っておきたい。まずSMの構成としては、Kepler世代と同様にGP104でもDP Unitを実装しつつ、無効化するだろう。これはDark Silicon絡みが理由だ。

ひょっとするとGP104ではDP Unitを省くかと思ったのだが、GPUの場合は通常のコアがフル稼働するので、熱密度がすごいことになる。したがって、多少熱を発生しないユニットをダイ上に残すことで、熱密度を緩和する必要がある。DP Unitはこの目的には手頃であり、またSMの再設計の手間を省くという意味でも有用だろう。

次がSM数であるが、GM204が28nmプロセスでおよそ300mm2程度だった。生産コストを抑えることを考えると、400mm2はかなり厳しいところであり、350mm2前後と仮定すると、SMの数は多くて36個(2304コア)あたりだろう。

GM204の2048コアに比べるとあまり差がないが、P100ですらベースで1.3GHz駆動が可能だったため、SM数を抑えたGP104では1.5GHzあたりも可能かもしれず、さらにWarp数を増やしたことで効率が改善しているため、性能もその分引き上げられると思われる。

問題はメモリー帯域だ。GP100では4FLOPS/Bytesを目指しており、実際はもう少し少ない(単精度で言えば10TFLOPS/1TBytesなので、10FLOPS/Byteの計算になる)あたりでバランスしている(4FLOPS/Byteとのギャップは2次キャッシュで埋める)形だ。もしGP104でも同程度の帯域を実現するとすると、おおよそ700GB/秒程度の帯域が必要になる(2304コア/1.6GHz動作で試算)。

これがGDDR5Xで可能か? というと、一応ぎりぎり可能ではある。GDDR5Xは、すでにMicronが14Gbps動作の型番をラインナップしており、14Gbps/384bit構成なら帯域は672GB/秒でほぼ700GB/秒が実現できるからだ。

512bit幅までやれば、900GB/秒近い帯域が確保できる。もっともこのクラスならそろそろHBM2を考えたほうがマシだとは思うが。以上のことから、2016年6月登場予定のGeForce GTX 1080相当のスペックはこれに準じたものとした。

またGeForce GTX 1070相当のものは、おおむねGeForce GTX 980と同等のシェーダー構成で動作周波数をやや引き上げたあたりでバランスさせてみた。この構成では、GDDR5Xは12Gbpsのものでも間に合う計算になる。もっともこのあたりは完全に筆者の推定なので、よく眉につばをつけて見ていただきたい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ